# **EMBEDDED SYSTEMS**

BASED ON CORTEX-M4 AND THE RENESAS SYNERGY PLATFORM

#### 2020

PROF. DOUGLAS RENAUX, PHD PROF. ROBSON LINHARES, DR. UTFPR / ESYSTECH

RENESAS ELECTRONICS CORPORATION

# 12 WEEK COURSE OUTLINE (1/2)

- 1) Introduction

- What are embedded systems

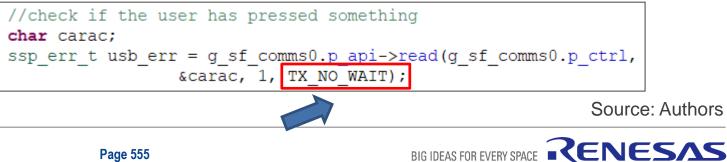

- Characteristics

- Sample Market Segments

- The IoT Era

- 2) Computer Architecture

- RISC vs CISC

- 3) ARM Cortex-M Architecture

- Block Diagram

- Registers

- Instruction set

- Memory access

- Exception handling

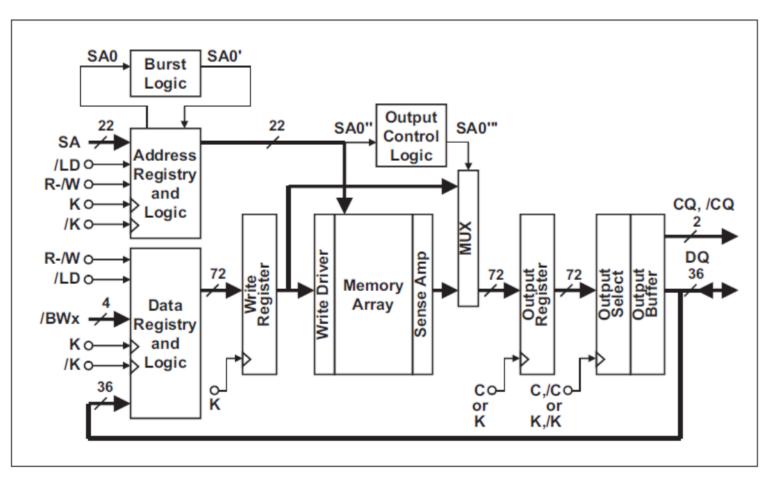

- 4) Memory

- SRAM

- DRAM (SDRAM, DDR)

- ROM/EEPROM/Flash

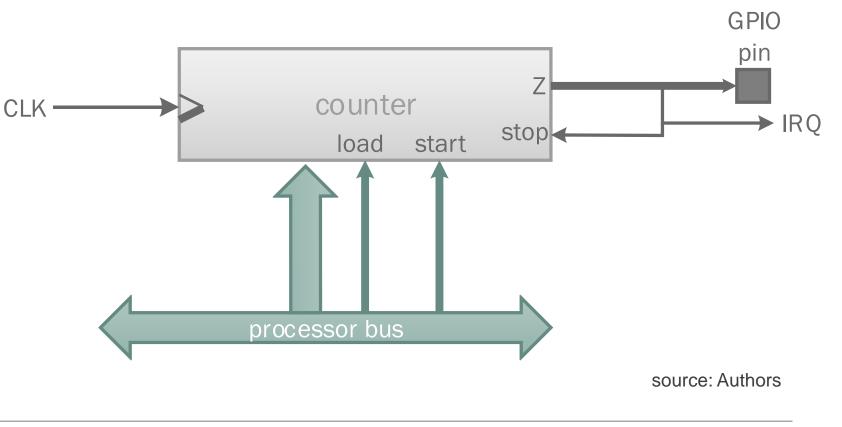

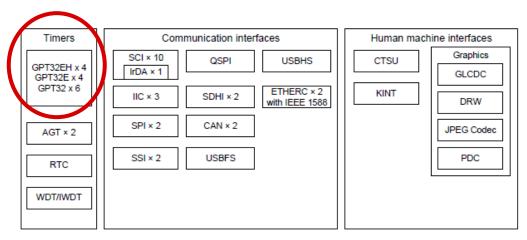

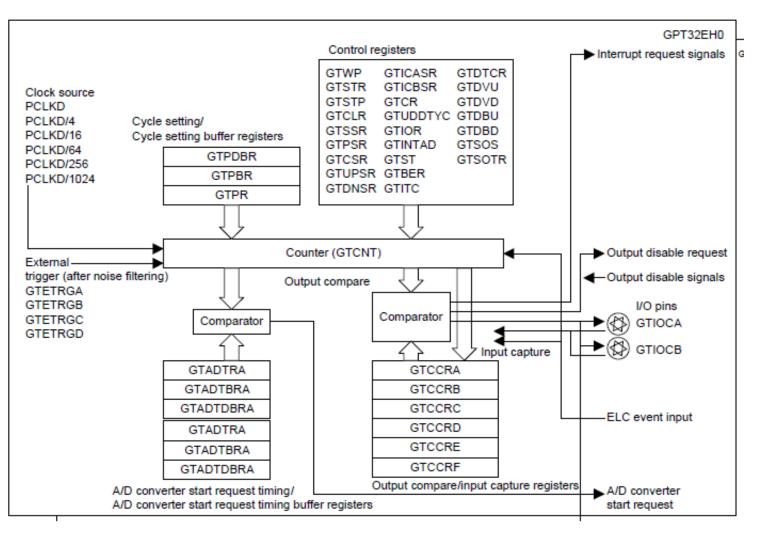

- 5) Timer and GPIO

- Timer

- PWM

- GPIO

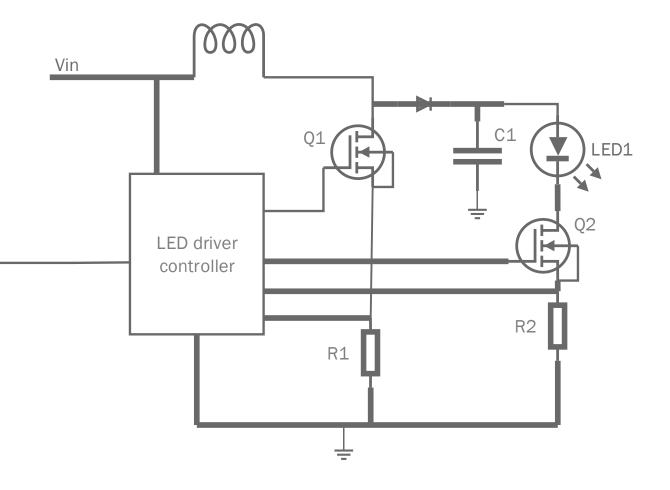

- Simple drivers (e.g. LED, Relay)

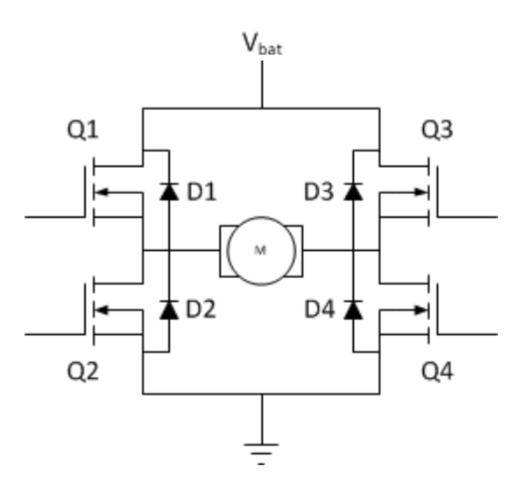

- Power drivers (motors)

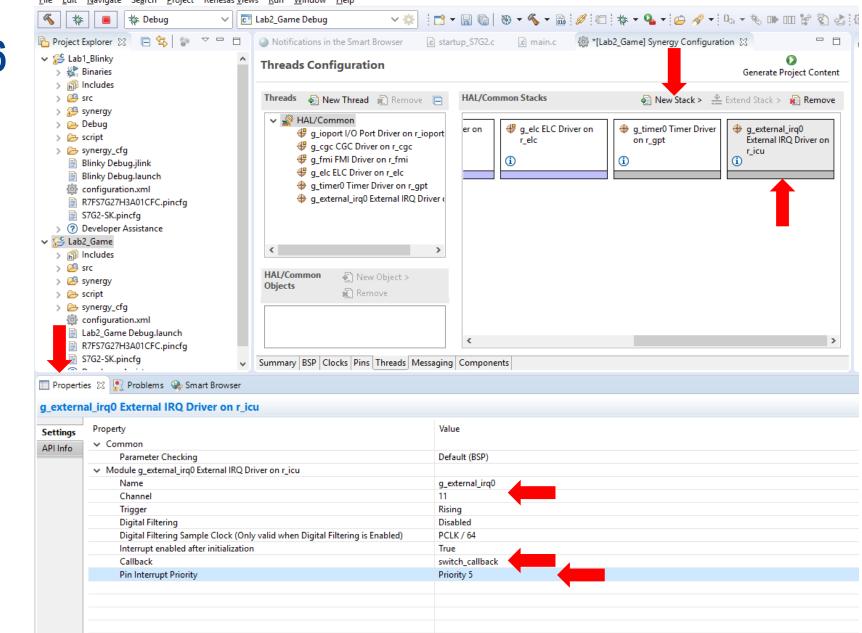

- 6) Interrupt Controller

# 12 WEEK COURSE OUTLINE (2/2)

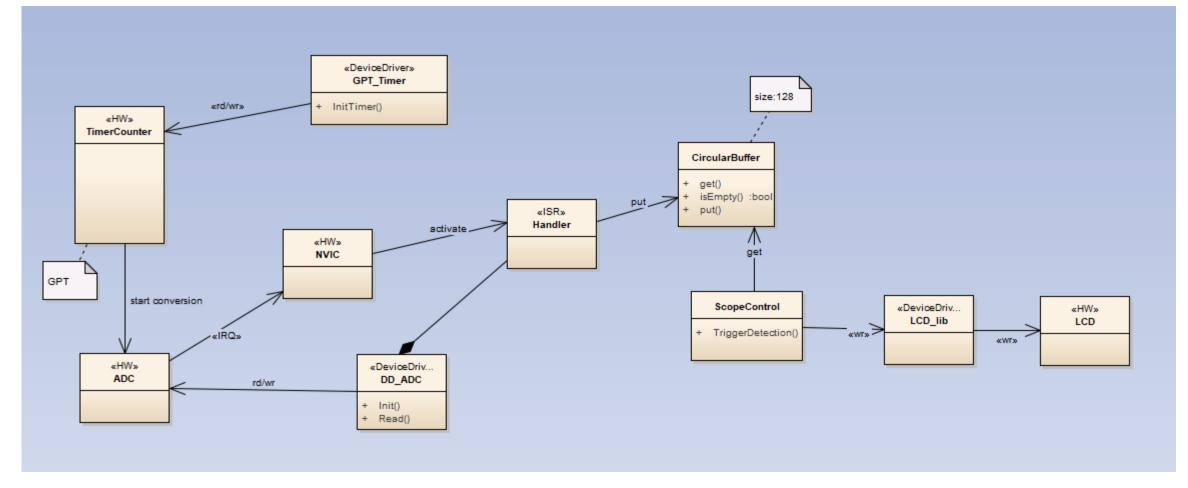

- 7) Analog Interfacing

- ADC / DAC

- 8) Serial Communication

- UART

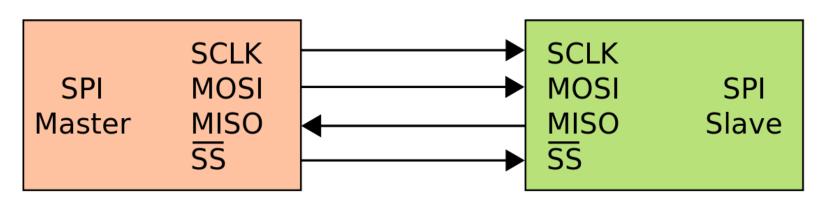

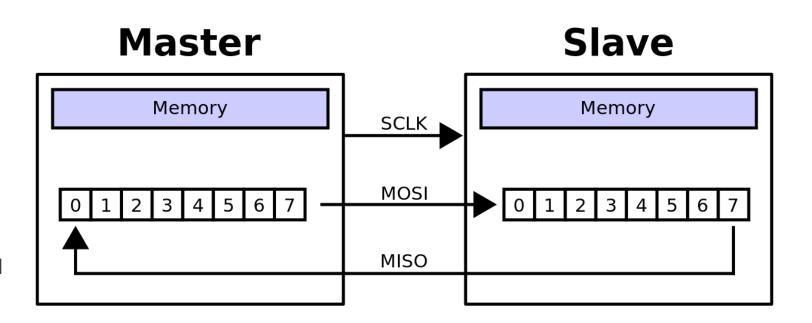

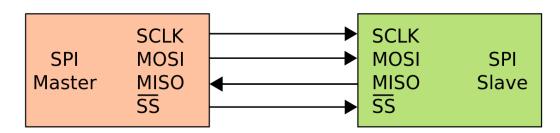

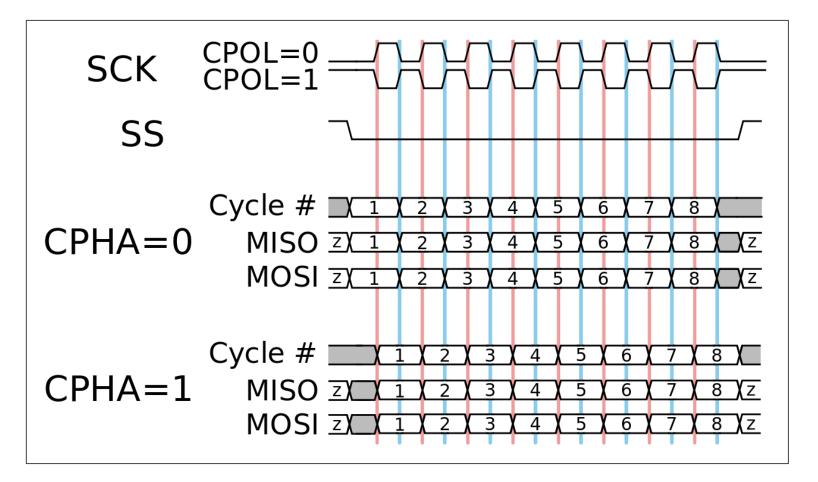

- SPI

- I2C

- 9) CAN

- Physical interface

- Stack

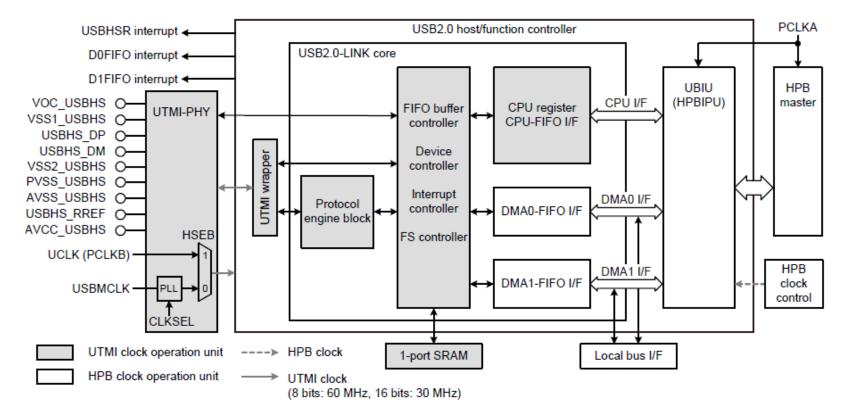

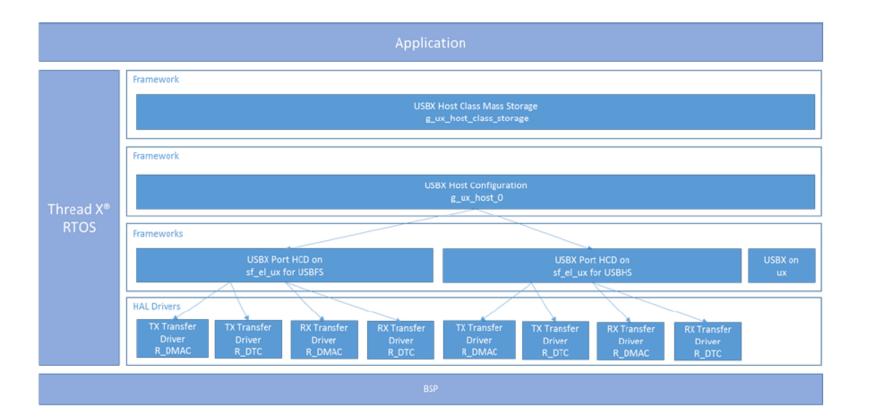

- 10) USB

- Physical interface

- Stack

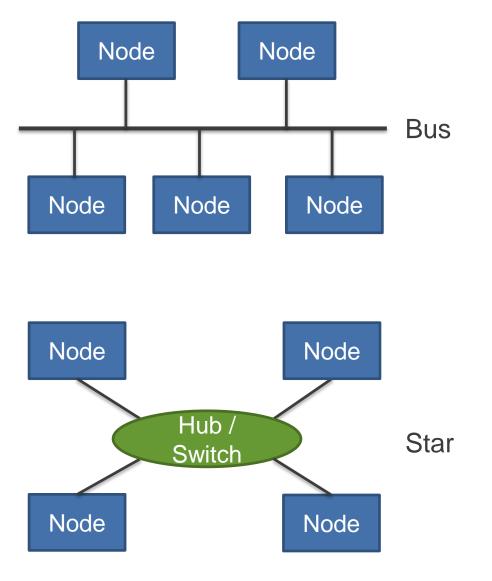

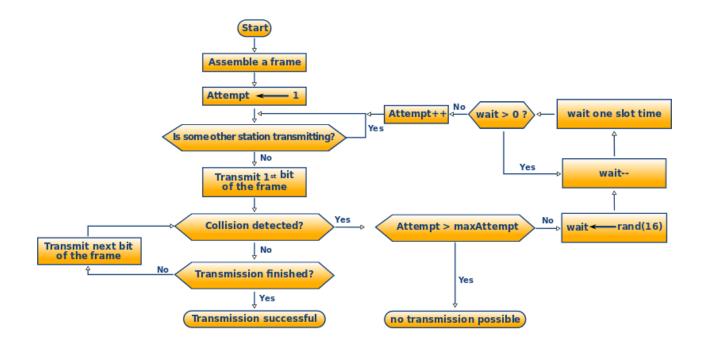

- 11) Ethernet

- Physical interface

- Stack

- 12) Software Development

- Software Process

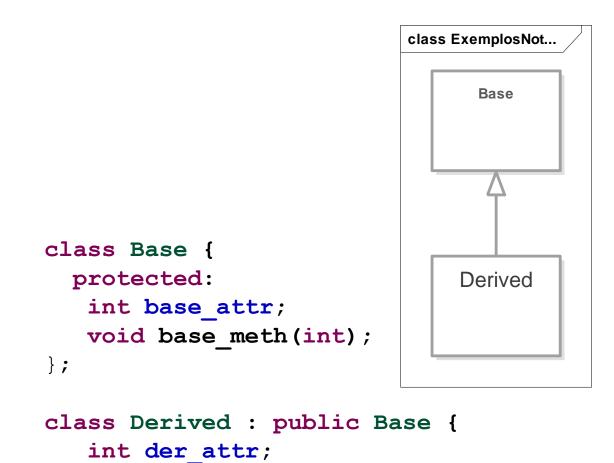

- UML Class Diagram

- UML State Machine Diagram

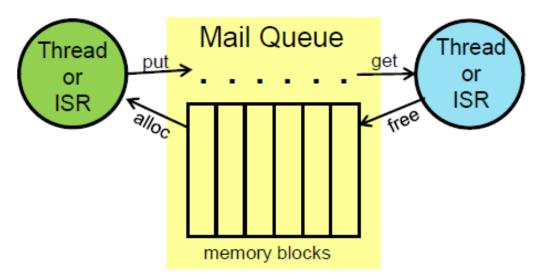

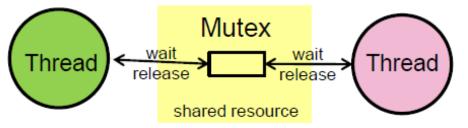

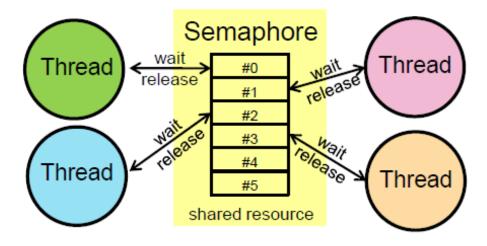

- 13) Concurrent Programming

- Tasks / Context Switching, Scheduling

- Semaphores, Signals / Messages

- Common problems to avoid: deadlock, priority inversion

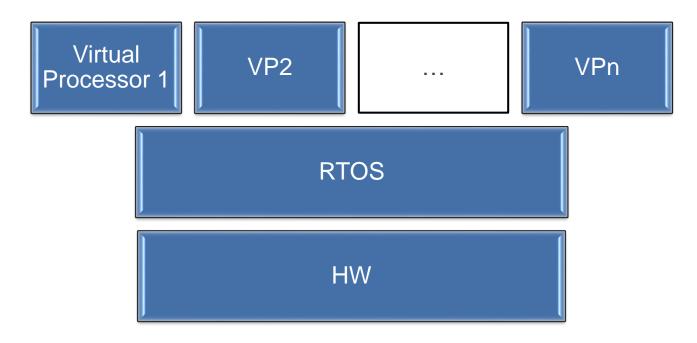

- 14) RTOS

- Thread Management

- Inter-thread communication and synchronization

- Timing Services

- Memory Management

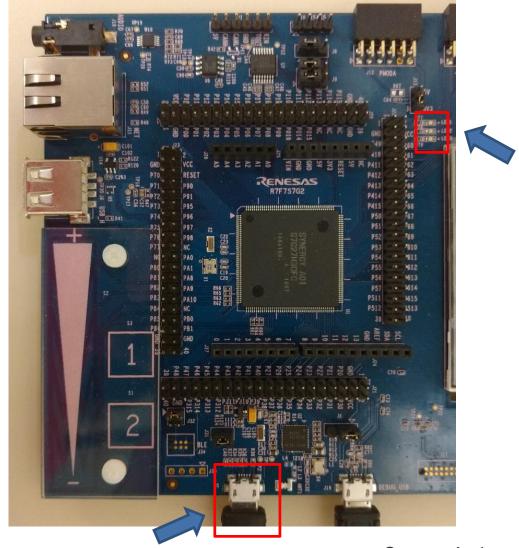

#### LIST OF LABS – BASED ON SK-S7G2

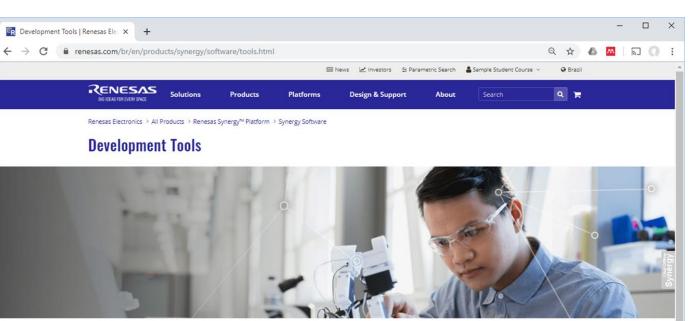

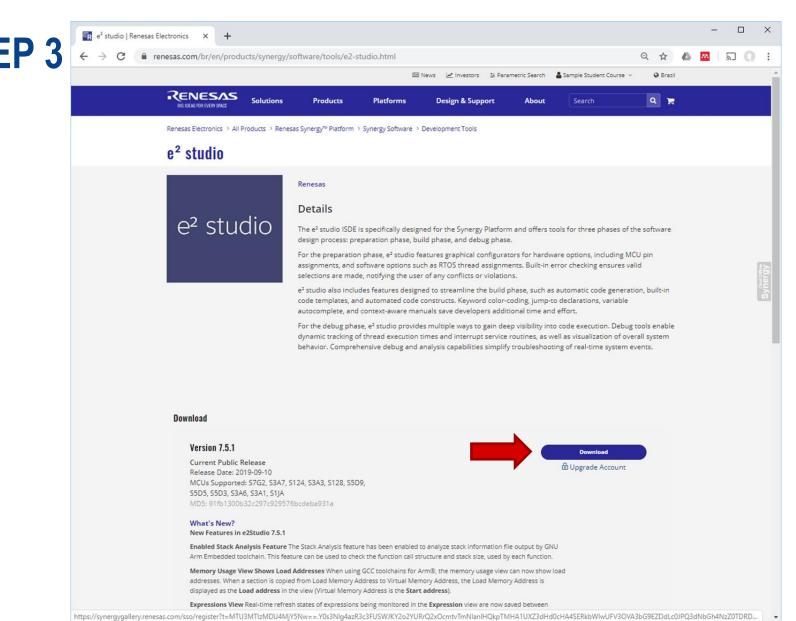

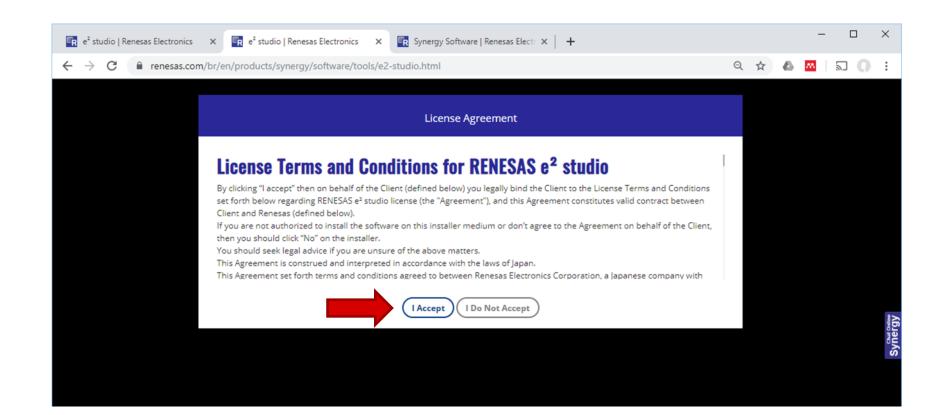

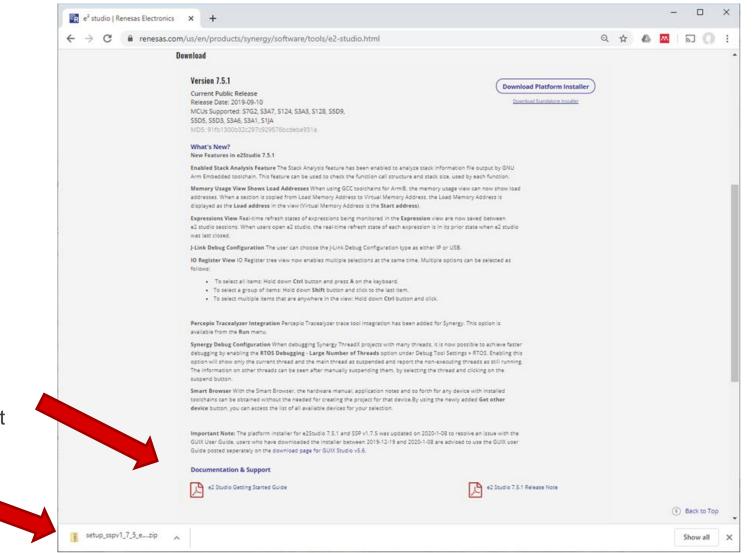

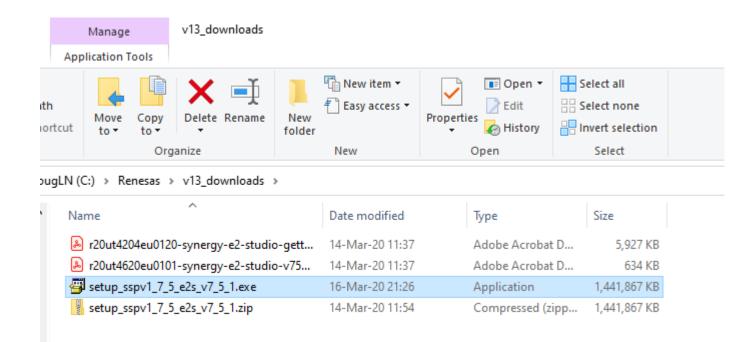

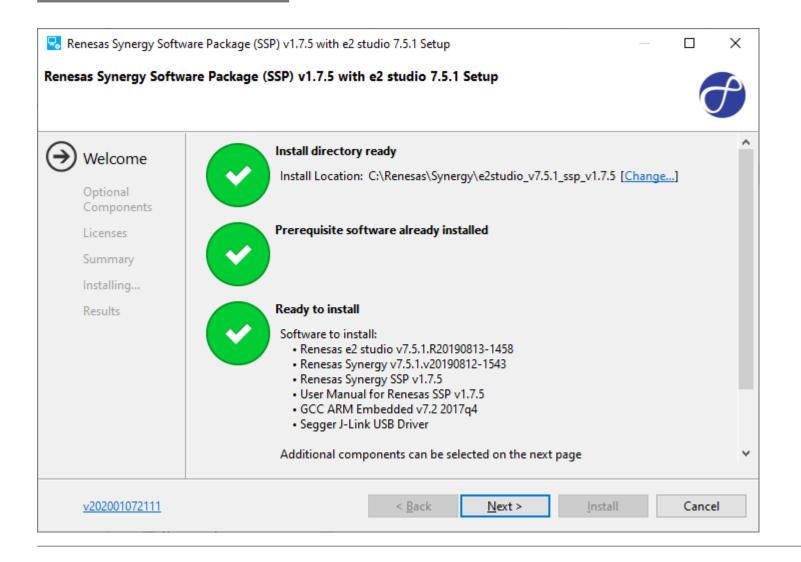

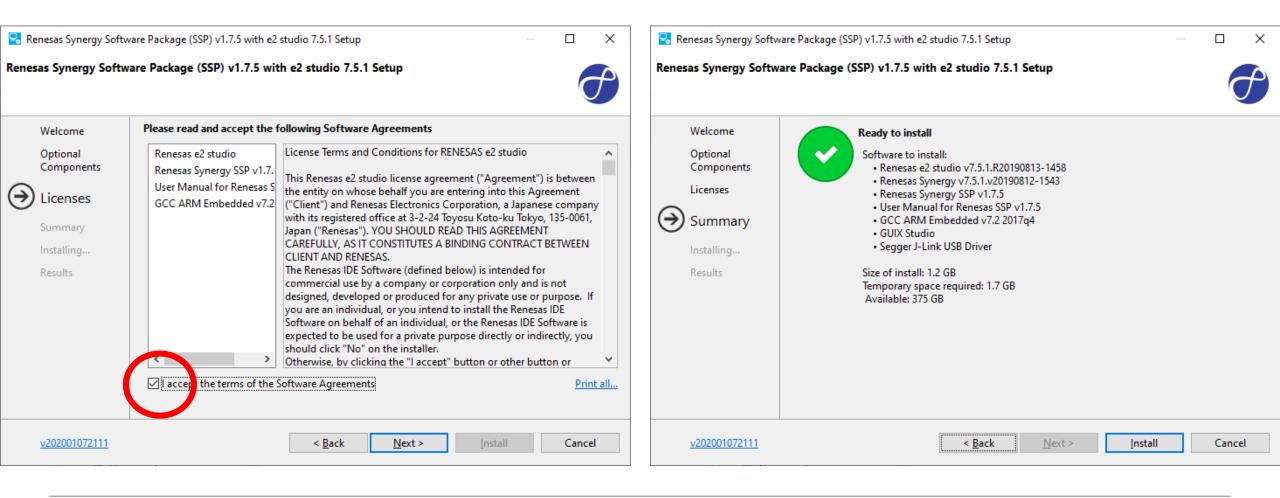

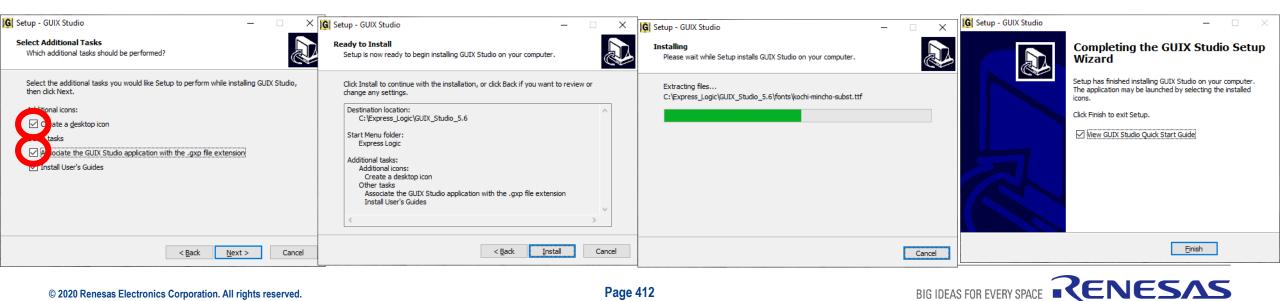

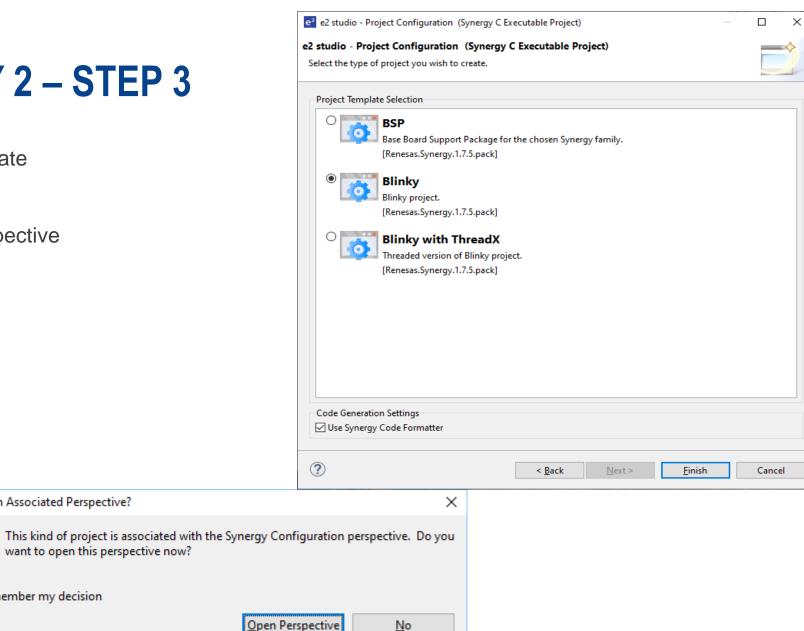

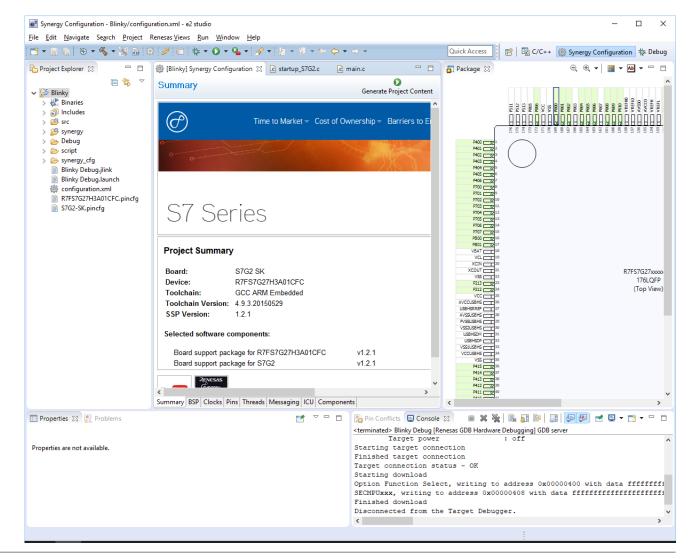

- Lab1 Synergy Installation try demo program on the S7G2 board. Requirements: none.

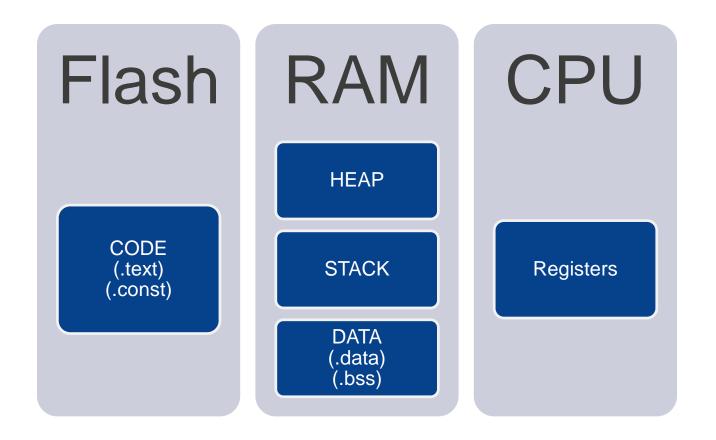

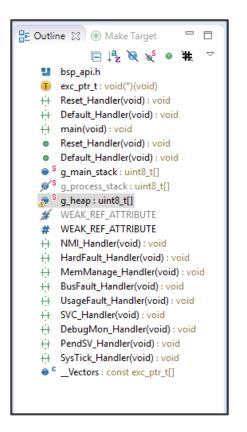

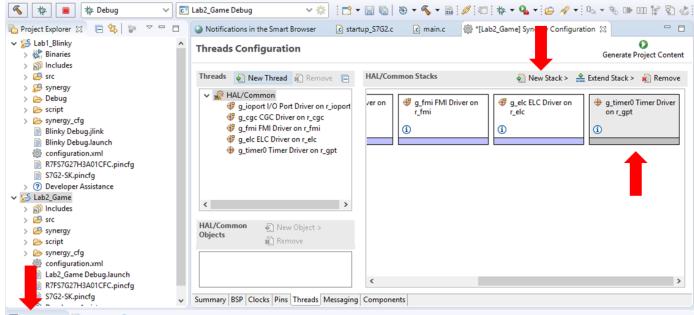

- Lab2 Sample C program means to access hardware peripherals; memory organization of a C program. Requirements: Section 5.

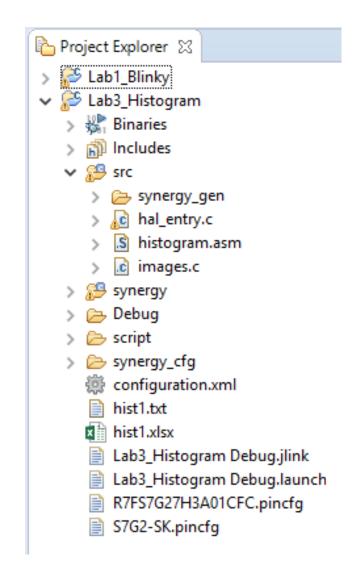

- Lab3 Assembly Programming ATPCS access from C a function written in assembly. Requirements: Section 5.

- Lab4 Peripheral Sample device driver. Requirements: Section 6.

- Lab5 Serial Communication. Requirements: Section 8.

- Lab6 Display and Touch. Requirements: Section 8.

- Lab7 RTOS. Requirements: Section 14.

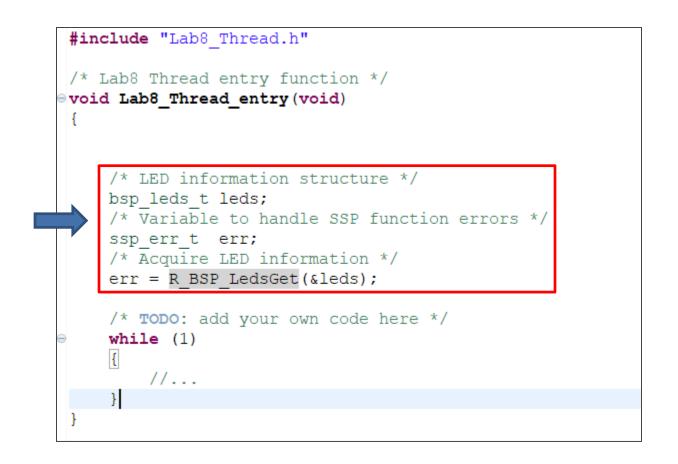

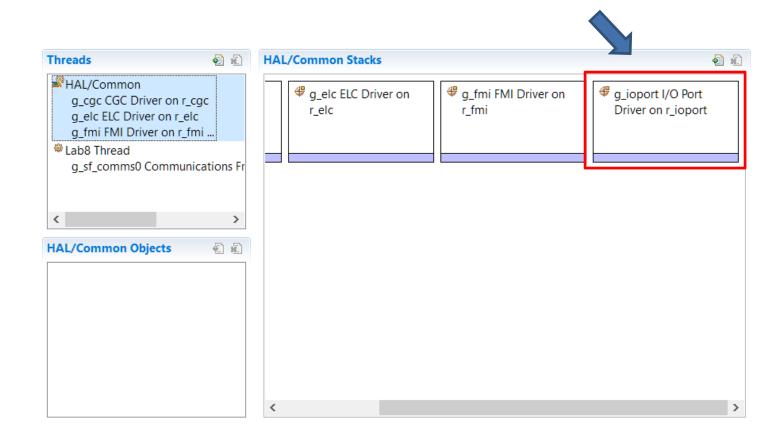

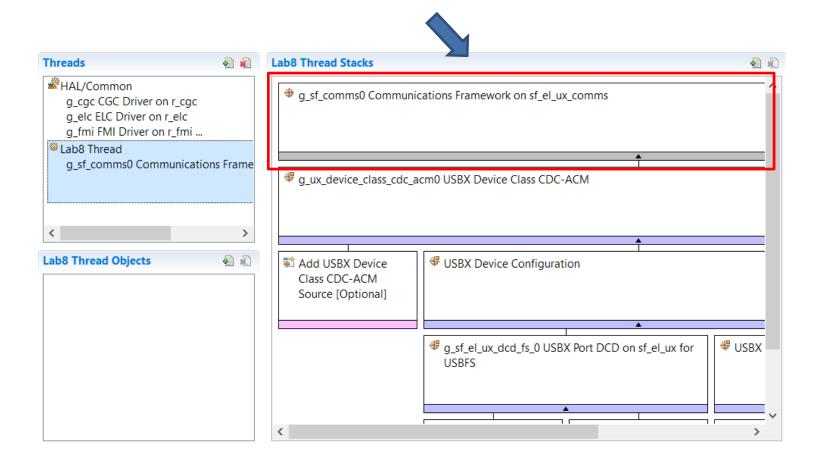

- Lab8 USB Device. Requirements: Section 14.

- Lab9 IoT. Requirements: Section 14.

- This course material was developed to contribute to the several forms of training in the area of Embedded Systems, but particularly with undergraduate courses such as Electrical Engineering, Computer Engineering and Computer Science.

- Contents can be freely copied and distributed to students both for commercial and non-commercial purposes, as long as:

- Credit to original work mentioning authors and Renesas as the distributor of this work.

- The contents can be freely modified to suit the needs of specific courses, all figures made by the authors may be freely used without modification as long as credited; likewise, all figures authored by Renesas may be freely used without modification as long as credited. All figures from other sources, if used in derived work or in other works must request authorization from the original author/copyright holder.

- The authors: Douglas Renaux and Robson Linhares are faculty at UTFPR in the subjects of Embedded Real-Time Systems and Computer Architecture and Organization.

UTFPR is the Brazilian Federal University of Technology.

- eSysTech Embedded Systems Technologies is a company providing engineering and training services in the area of Embedded Systems. It is a spin-off of the Laboratory of Innovation and Technology in Embedded Systems of UTFPR.

- Renesas is a major player in the semiconductor market. They have been providing significant support for educational material such as this one. Renesas has worldwide non-exclusive distribution rights for this material.

### **OVERVIEW AND PREREQUISITES**

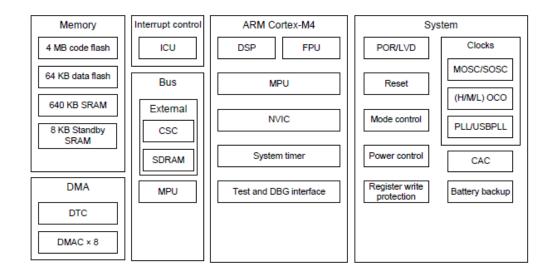

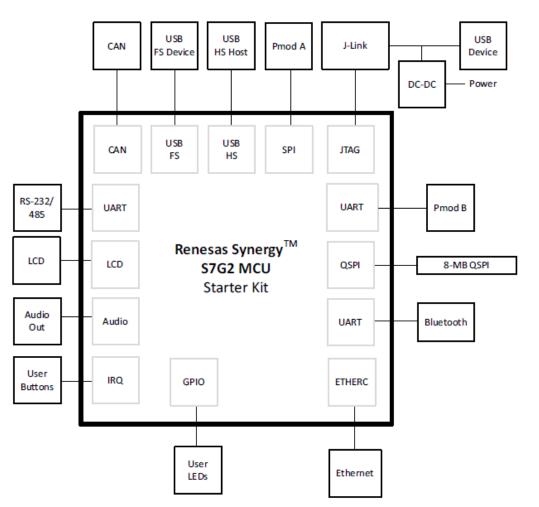

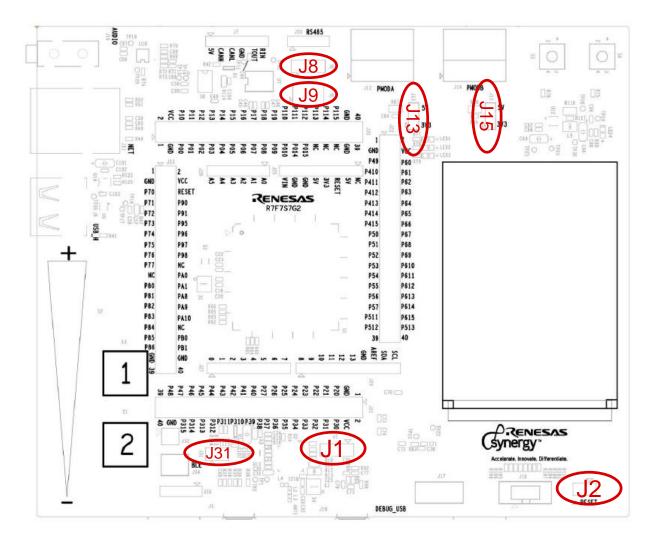

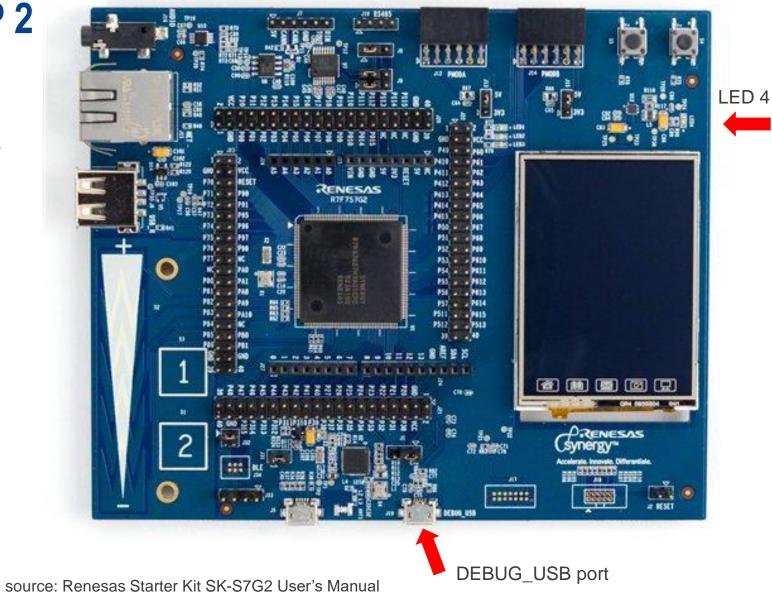

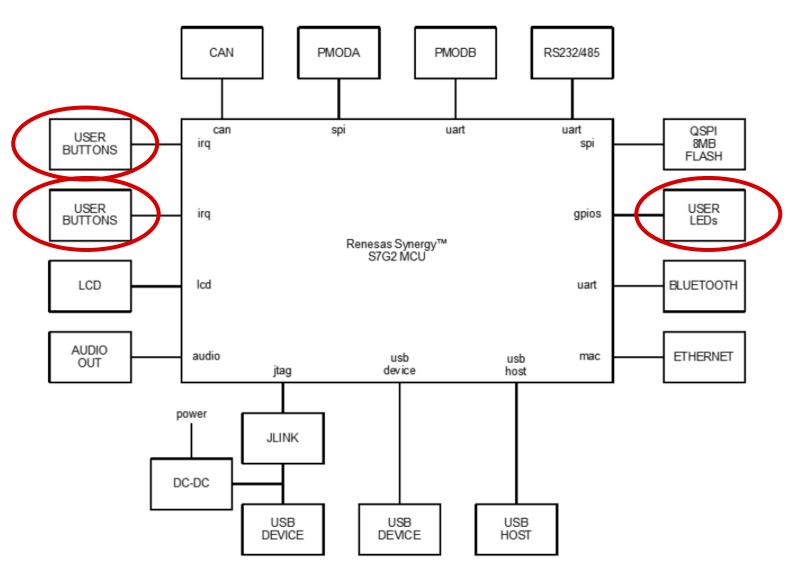

- This Embedded Systems course is organized into theory and practice parts. There are 12 theory sections and 9 labs. The labs solutions can be made available to instructors. All labs are conceived to be developed on the Renesas SK-S7G2 board, based on an ARM Cortex-M4F MCU.

- The course assumes that the students have previous knowledge on:

- C programming for embedded systems

- Microcontrollers and assembly programming (on an architecture other than ARM)

- Digital Systems

- Digital communications and networks

# **1 – INTRODUCTION**

- 1. What are Embedded Systems

- 2. Characteristics

- 3. Market Segments

- 4. The IoT Era

#### WHAT ARE EMBEDDED SYSTEMS?

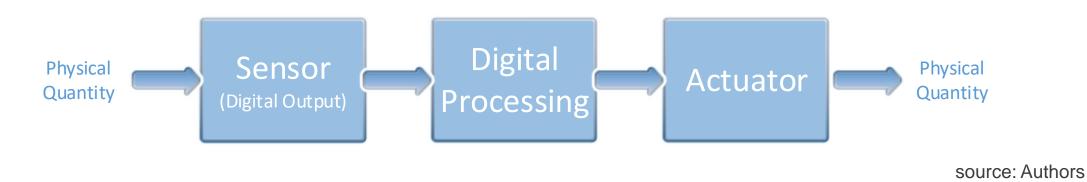

An Embedded System (a.k.a. Embedded Computing System) is a computing system that is built-into (i.e. embedded) a larger device, such as an equipment, a system, or a vehicle.

Embedded Systems (ES) are usually application-specific and have real-time constraints; thus, many ES are also real-time systems. Often, ES are used in control loops: reading sensors, processing data, and generating outputs that control the device they are embedded into. Finite State Machines are commonly used to model the behavior of ES.

# **CHARACTERISTICS OF EMBEDDED SYSTEMS (1/4)**

Typical characteristics of an Embedded System are:

1. Microcontroller based system consisting of a processor,

non-volatile memory (Flash), volatile memory (RAM), and a large number of inputs and output interfaces as well as communication channels.

- 2. Cost effective implementations as many device architectures are cost-driven.

- 3. Energy efficient solutions as many devices are battery powered. Current trend is to develop battery-less devices that harvest energy from the environment.

### **CHARACTERISTICS OF EMBEDDED SYSTEMS (2/4)**

- 4. Heterogeneous. While desktop computers are based on standard platforms (Windows PC, Apple IOS, ...) there is a large variety of hardware and software for embedded systems.

- 5. Variety of restrictions to the design solutions, such as:

- a) Physical: Size, Weight, Temperature Range, Vibration, Dust, Spills, Water;

- b) Computational resources: processing speed, non-volatile memory, RAM, available I/O;

- c) Response time.

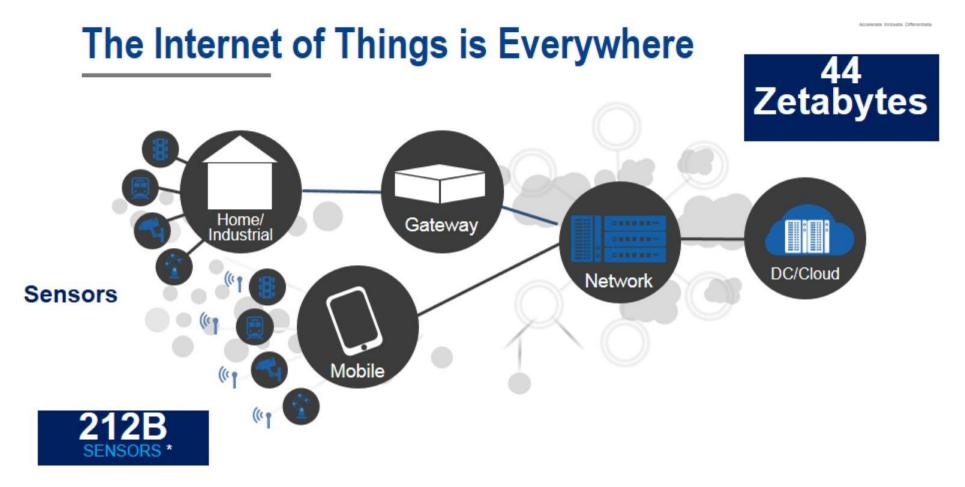

- 6. Interconnected. Embedded devices and systems are ever more interconnected to each other. Trend is to increase the interconnection rate (IoT).

# **CHARACTERISTICS OF EMBEDDED SYSTEMS (3/4)**

#### 7. Reliability

The ability of a system or component to function under stated conditions for a specified period of time.

#### 8. Availability

The ability of a system or component to function at a specific moment of interval of time.

#### 9. Maintainability

Measures how easily and how fast a system can be restored to operational status after a failure.

#### **10.** Testability

The degree to which a system or component facilitates the establishment of test criteria and the performance of tests to determine whether those criteria have been met.

# **CHARACTERISTICS OF EMBEDDED SYSTEMS (4/4)**

#### **11.** Scalability

The ability of a system to handle increased workload by repeatedly and cost-effectively adding components to extend the system's capacity.

#### 12. Safety

Concerns the requirement: not to harm people, the environment or other assets.

#### **13.** Security

The ability of a system to protect information and system resources with respect to integrity and confidentiality.

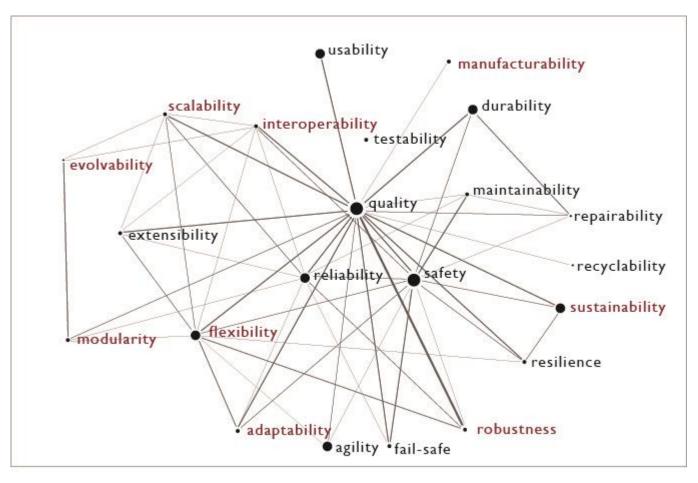

### **CHARACTERISTICS OF EMBEDDED SYSTEMS**

Relationship among 22 of the most common ilities:

BIG IDEAS FOR EVERY SPACE **RENESAS**

to read about this graph: Book Chapter about the Ilities: Chapter 4 from "Engineering Systems: Meeting Human Needs in a <u>Complex Technological World</u>" by de Weck O., Roos D. and Magee C, MIT Press, January 2012 (http://strategic.mit.edu)

### SAMPLE MARKET SEGMENTS

- Consumer Electronics

- Telecommunications

- Home Automation

- Industrial Automation

- Transportation

- Avionics

- Navigation

- Electric Vehicles

- Defense

- Medical Equipment

- ??? (many new areas to come)

Smart House

**Connected Care**

Smart Factory

**Cool Gadget**

Robots

source: Renesas DevCon2015

\_\_\_\_\_

# **CONSUMER ELECTRONICS**

- Phones

- Videogame consoles

- Printers

- Digital cameras

- Audio/Video:

- Television

- Music Players

- Home Entertainment Systems

- BRD players

source: pixabay.com (CC)

### **HOUSEHOLD APPLIANCES**

- Washing Machines

- Dishwasher

- Air Conditioners

- Microwave Oven

source: pixabay.com (CC)

#### **TELECOMMUNICATIONS**

- Routers

- Satellite Phones

- Switches

source: wikimedia.org (CC)

source: pixabay.com (CC)

#### HOME AUTOMATION

source: pixabay.com (CC)

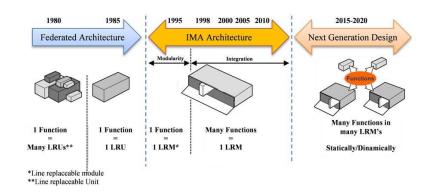

#### **TRANSPORTATION – AVIONICS**

Glass cockpit of the

Airbus A350 XWB

source: flickr (CC)

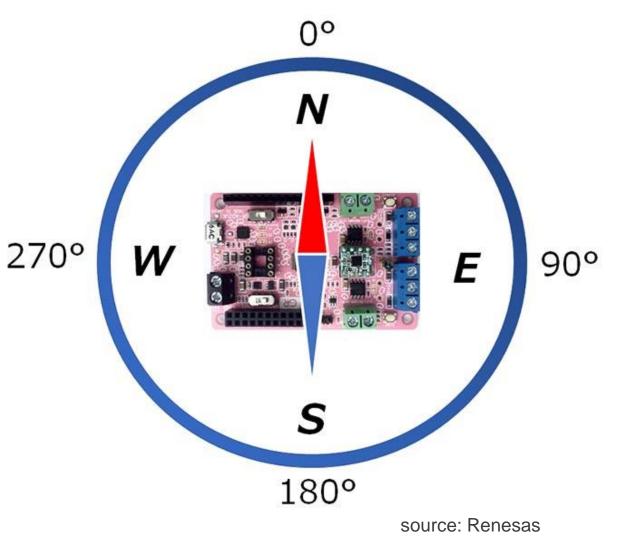

### **TRANSPORTATION – NAVIGATION**

- Automotive GPS

- Electronic Compass

### **TRANSPORTATION – AUTOMOTIVE**

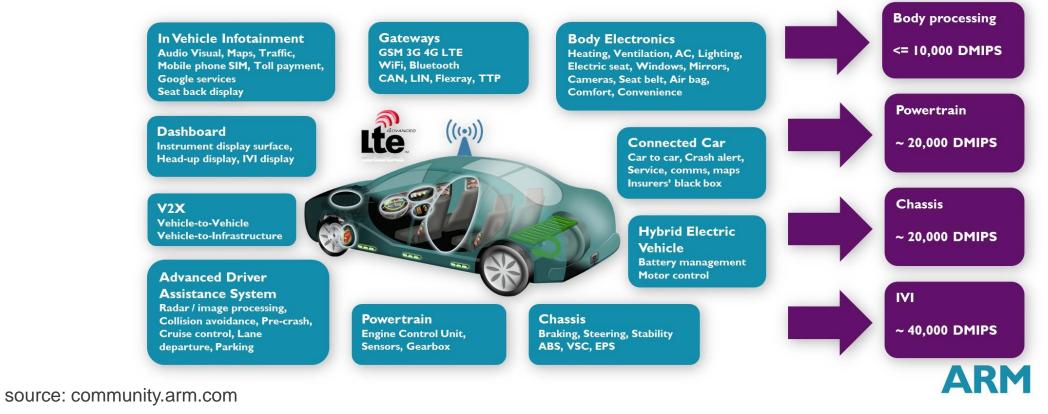

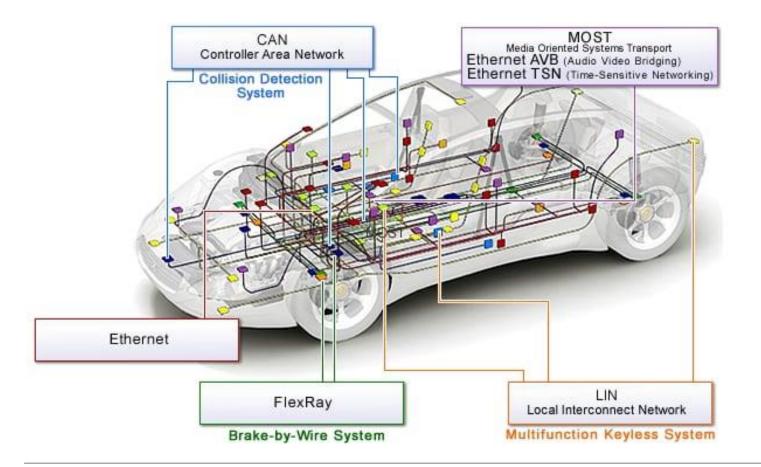

#### Automotive ECUs Controllers by 2020

- Between 25 and 100 individual ECUs

- With distributed sensors and motor controllers.

© 2020 Renesas Electronics Corporation. All rights reserved.

#### **TRANSPORTATION – AUTOMOTIVE**

source: Renesas

# **MEDICAL EQUIPMENT**

- CT Scanners

- ECG (Electrocardiogram)

- Blood Glucose Monitor

- Blood Pressure Monitor

- Body Composition Analyzer

#### HEALTHCARE SOLUTION USING RENESAS SYNERGY™

Accelerate Medical Device Design with IEC62304 Class C Pre-Certified Renesas Synergy™ Platform Safety Solution

# Certified 100 18

source: Renesas

THE IOT ERA

source: Renesas

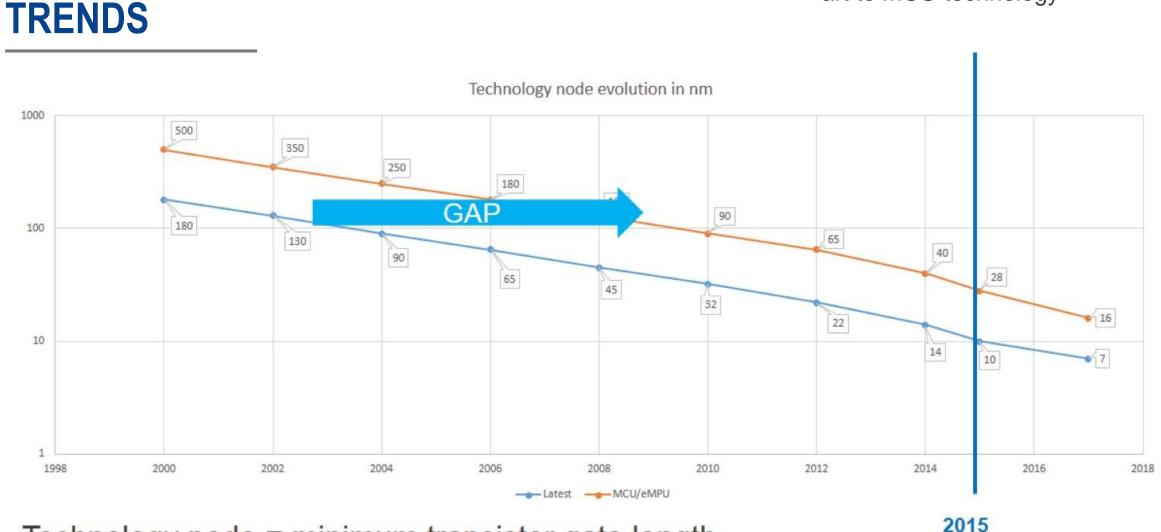

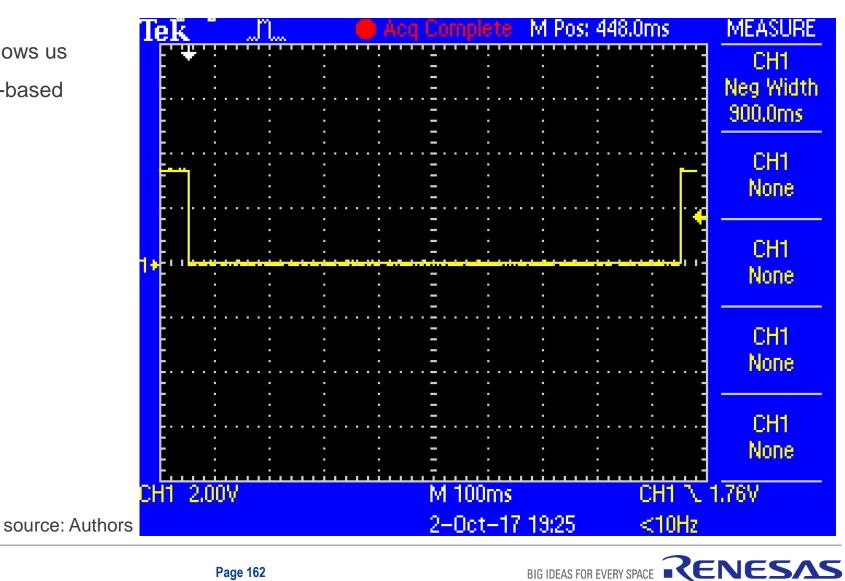

Five-year gap from state of the art to MCU technology

#### Technology node = minimum transistor gate length

Source: ITRS, Renesas Electronics - based on product announcement

source: Renesas

© 2020 Renesas Electronics Corporation. All rights reserved.

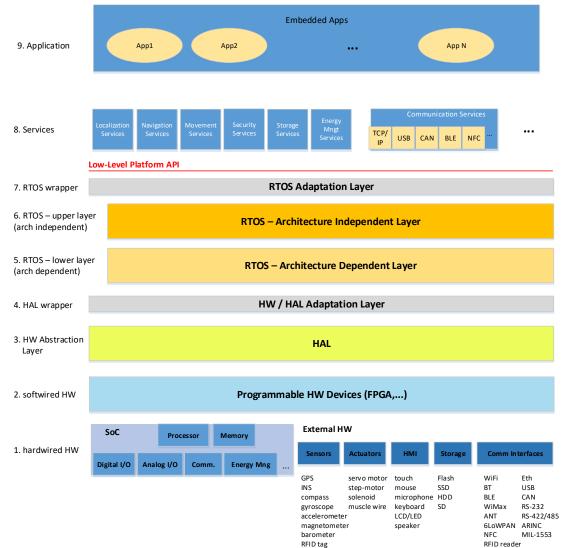

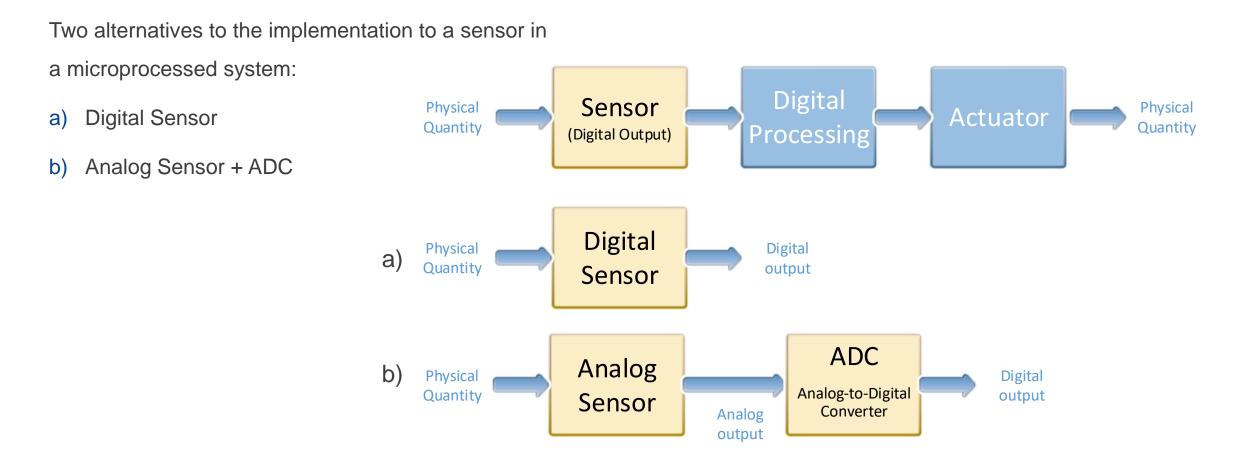

### **EMBEDDED SYSTEMS ARCHITECTURE – GENERIC MODEL**

- One of the important characteristics of Embedded Systems (ES) is its diversity. Hence, a truly generic model for an ES does not exist.

- The model presented here attempts to represent a large set of the existing ES. Hence, it is adequate to understand Embedded Systems concepts.

suggested reading: (see IEEEXplore.ieee.org)

D. Renaux, F. Pottker, "<u>Applicability of the CMSIS-RTOS Standard to the Internet of Things</u>", 10th Workshop on Software Technologies for Future Embedded and Ubiquitous Systems - SEUS/ISORC 2014, June 2014.

#### **EMBEDDED SYSTEMS ARCHITECTURE GENERIC MODEL**

source: Authors

# **1. HARDWIRED HW**

- This level is composed of hardware devices (MCU, Memory, I/O, connectors) whose connection is determined by the copper traces on a PCB, hence, not changeable after fabrication.

- Currently, a significant portion of the HW functionality of an ES is integrated into a SoC (System on Chip).

External HW consists of the remaining HW not in the SoC and comprises, among others, sensors, actuators, Human-Machine Interface devices, Storage devices, and a large variety of communication interfaces.

Skywire Renesas Synergy PMOD Kit

# 2. SOFT WIRED HW

- In contrast to Level 1, the soft wired HW level consists of components whose connection is programmable, hence, can be modified at any time.

- Currently, the most common programmable devices are FPGAs, however, a variety of programmable logic devices (PLD) are available: FPGA, CPLD, GAL, PAL, PLA, and even ROM.

- The two hardware layers (1 and 2) compose the physical part of an embedded system. The remaining layers (3 to 9) are software layers.

### **SOFTWARE LAYERS**

The upper layers (3 to 9) are software layers.

Embedded Systems Software have two distinct characteristics:

- 1. Typically the development environment (compiler toolchain) generates a single binary file that integrates all software components: device drivers, libraries (RTOS, Services, ...) and the Application. Hence, avoiding the process of reading an executable file and loading it on memory.

- 2. While on desktops applications are changed and upgraded quite frequently, in embedded systems, typically a single multitasking application is executed along the life of the device. Upgrades may occur but are much less frequent.

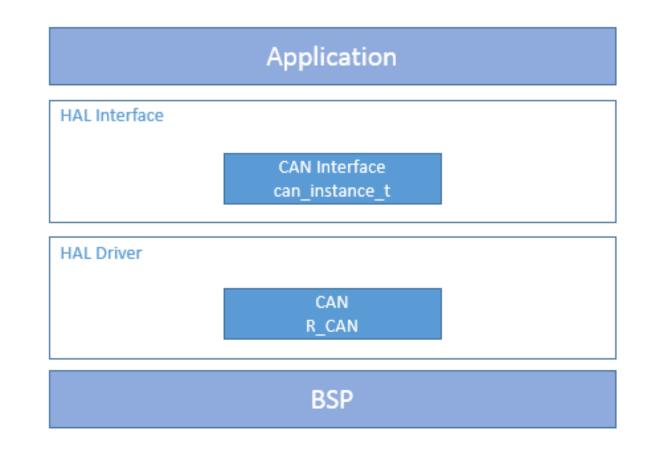

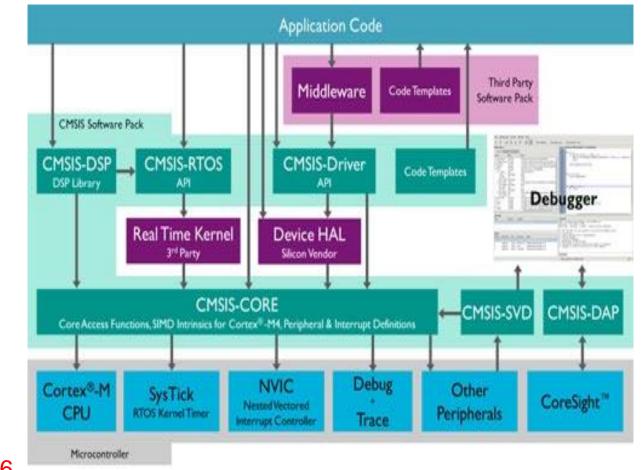

### 3. HARDWARE ABSTRACTION LAYER

- The HAL is comprised of a set of functions that directly access the hardware devices. These functions are also called device drivers.

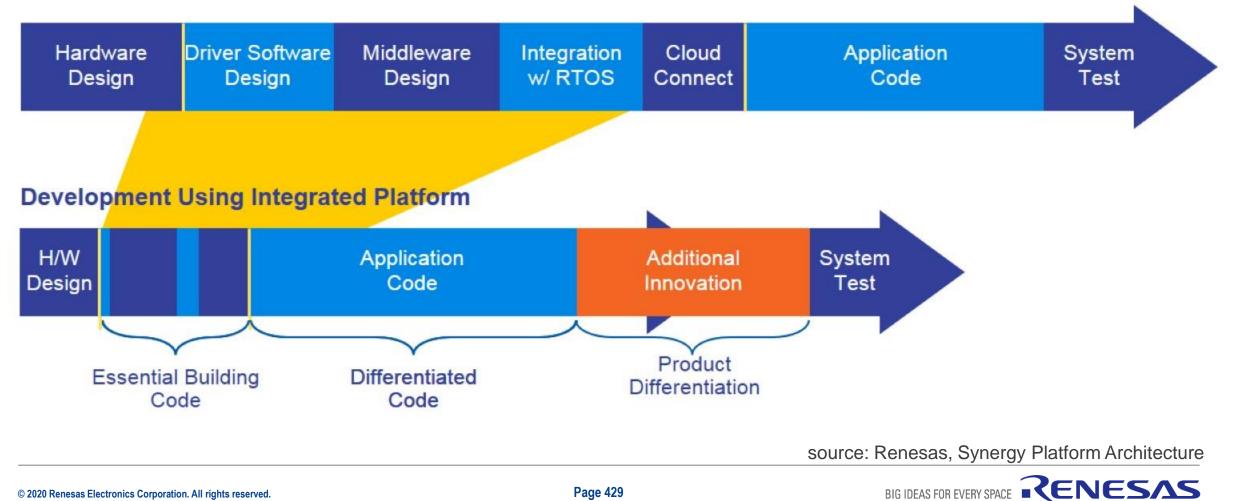

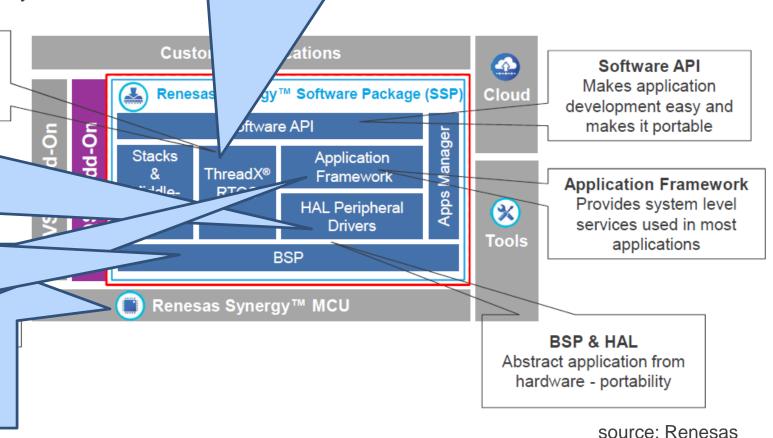

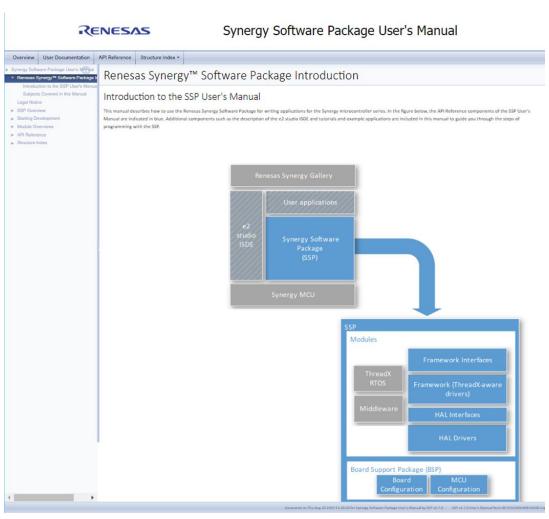

- A well-designed HAL provides to the upper levels a standardized interface, providing an easy interchange of devices. For instance, if all communication devices have the same API then replacing a comm. interface (such as SPI) for another (such as I2C) is straightforward. The Renesas SSP (Synergy Software Package) is an example of such.

- Developing a device driver for the HAL requires expertise in both hardware and software. Such a development is a complex and time-consuming task typically performed in C and sometimes mixing with assembly language.

# **4. ADAPTATION LAYER**

• An Adaptation Layer (or Wrapper) is a means of providing a common interface for different device drivers.

- If a HAL is not carefully designed, or if device drivers from different vendors are integrated in the same solution, then the software interface to the upper level may not be regular, meaning that different devices have access functions with different signatures. Such a scenario poses severe difficulties for portability and changes.

- The adaptation layer is a simple translation layer aiming at converting the non-standard interface to a standardized one.

Such a translation can often be done at compile time, hence, not imposing any runtime penalty.

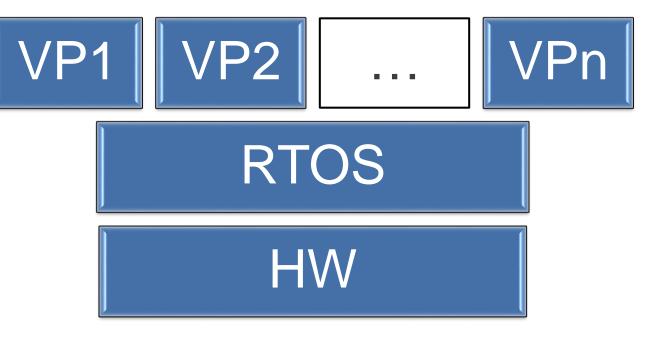

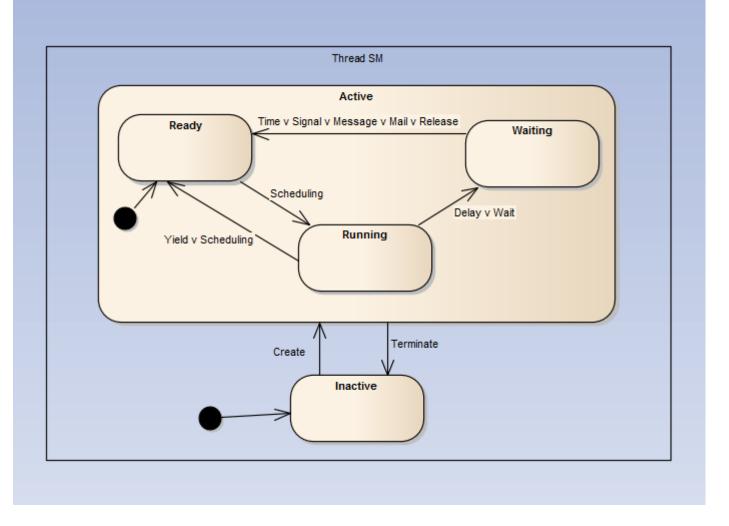

- Embedded Operating Systems have significant differences to O.S. used in desktop computers, including a very small memory footprint and a reduced amount of functionality. Most embedded O.S. have to provide support for real-time systems, hence, they are termed RTOS (Real-Time Operating System).

- The implementation of a well designed RTOS has at least two layers, so that different software modules implement the architectural dependent code and the architectural independent code. This approach improves modularity and improves the portability to other architectures.

# 7. RTOS ADAPTATION LAYER

This is a wrapper that translates the API of a given RTOS to a standard API, such as CMSIS-RTOS. Once a standard API is provided to the upper levels, all of the software in the Services and Application layers can be reused in different platforms without rewriting the calls to the RTOS.

- To cope with the large amount of functionality implement by software in current Embedded Systems, code reuse is almost mandatory. Thus, off-the-shelf software components are integrated to form the final solution. Typically, these components come in the form of libraries that are linked at compile time.

- A large variety of software components is available providing functionality for: TCP/IP stacks, USB stacks, communication protocols, georeferencing, navigation, security, storage, among many others.

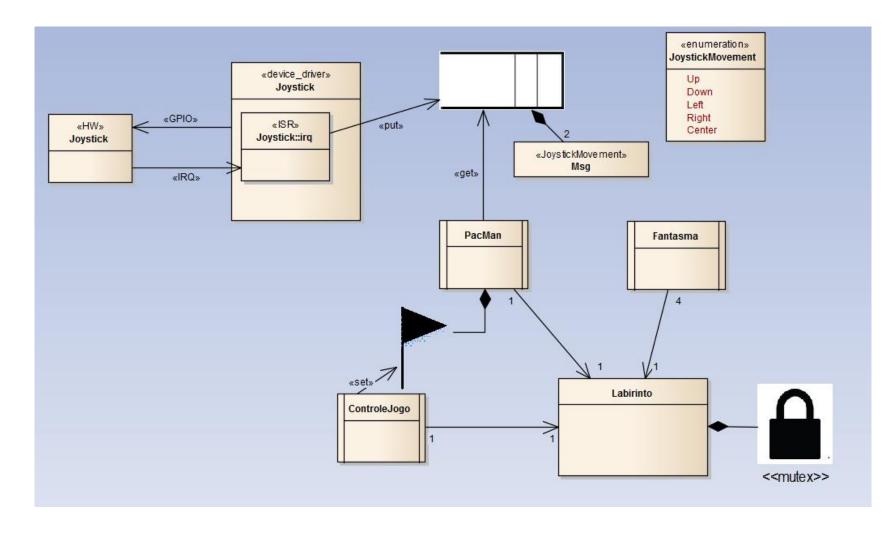

## 9. APPLICATION LAYER

- The top layer of the model is the Application Layer. This is the software layer that implements the specific functionality of each embedded system.

- In this layer, several concurrent tasks cooperate to provide the required functionality. Concurrent programming is the most common approach to cope with the software complexity of current Embedded Systems.

- The RTOS provides the management of the concurrency, among many other services.

## 2 – COMPUTER ARCHITECTURE – RISC VS CISC

- Computer Generations

- The RISC Paradigm

## **DEFINING "COMPUTER"**

Computer =

a device, or person, who performs a computation, i.e. a sequence of calculations according to an algorithm.

Hence, we consider Generation 0 of computers the generation that precedes the electronic device currently known as computer.

## **COMPUTER GENERATIONS**

| Generation | Description                                                                                             |

|------------|---------------------------------------------------------------------------------------------------------|

| 0          | Mechanical and Electromechanical Devices                                                                |

| 1          | 40's – Vacuum tubes<br>ENIAC, Zuse                                                                      |

| 2          | 50's – Transistors<br>Manchester University, IBM 350                                                    |

| 3          | 60's – SSI Integrated Circuits (logic gates)<br>Apollo Guidance Computer<br>IBM System/360, Digital VAX |

| 4          | 70's – Microprocessor                                                                                   |

| 5          | 2010's? – quantic / organic / optical???<br>Al                                                          |

## **RESEARCH PRECEDING THE RISC PARADIGM SHIFT**

- Careful examination of the execution of actual programs concluded that:

- Often, complex instructions were not used and the equivalent effect was obtained by a sequence of simpler instructions.

- The inclusion of a single complex instruction in the instruction set could impact overall performance by imposing a lower clock rate.

- Since the instructions did not have a regular execution sequence (i.e. each one had its execution determined by its microcode) the implementation of a pipeline was close to impossible.

## **RESEARCH PRECEDING THE RISC PARADIGM SHIFT**

What is the final goal?

- From the user's perspective, the goal is **performance of the application programs**

- RISC thesis: a processor whose instruction set is made of simple instructions with a regular execution, allowing the implementation

of a pipeline, will have a higher performance than a CISC

(Complex Instruction Set Computer)

John L. Hennessy ] David A. Patterson COMPUTER ARCHITECTURE A Quantitative Approach

1 : 1

RENESAS

M<

**BIG IDEAS FOR EVERY SPAC**

recommended reading: Computer Architecture: A Quantitative Approach 6th Edition by John L. Hennessy, David A. Patterson

## **RISC ARCHITECTURAL FEATURES**

Features that characterize the RISC paradigm are:

- An instruction set with a reduced number of very simple instructions.

- LD/ST architecture, meaning that only two instructions (and their variants) access memory: LD (load) reads data from memory, and ST (store) saves data to memory.

- All other instructions operate on registers. There is a large number of general-purpose registers, avoiding access to memory.

- All instructions follow the same logical execution sequence. Hence, a pipelined architecture can be implemented, significantly improving performance. Typically 1 instruction is executed every clock cycle.

Requirements for the implementation of a Pipeline in a processor:

- The instruction set must be designed so that all instructions have the same execution steps

- Instructions must be regular with respect to:

- Size

- Addressing modes

- Decoding

- Operands

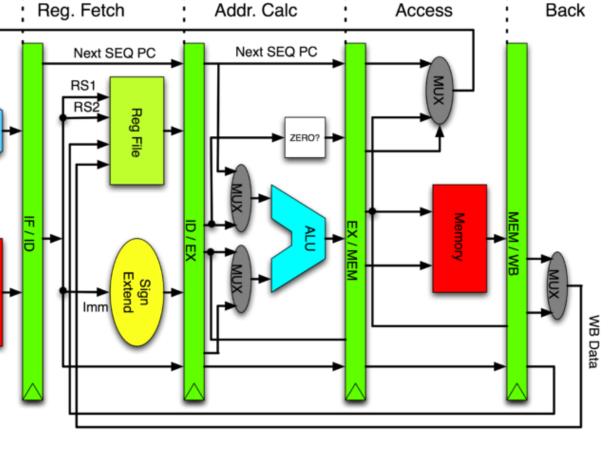

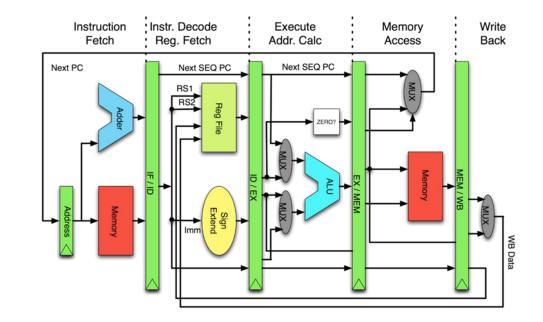

### PIPELINING

Example of a Pipeline with 5 stages:

1. Fetch

and 5

- 2. Decode and read operands in registers

- 3. Use ALU to execute instruction or to calculate memory address

- 4. Read or Write to memory

- 5. Write result back to Register file

Execute

source: wikimedia.org (CC)

Write

Memory

Instr. Decode

Instruction

Fetch

Adde

Next PC

## **BENEFITS OF PIPELINING**

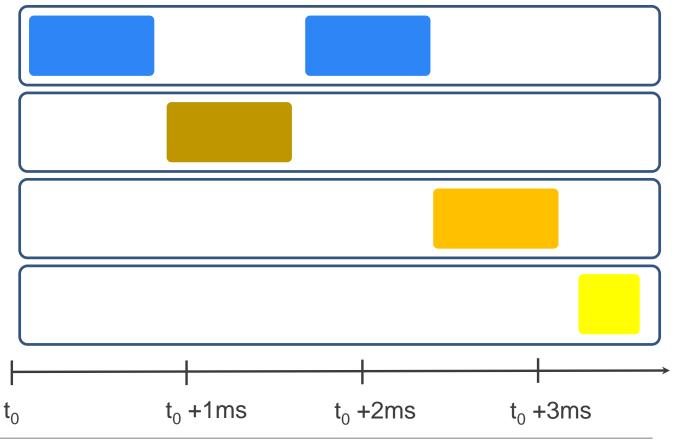

For the previous example of a 5 stage pipeline, the

execution over time is presented in this diagram.

Note that although each instruction takes 5 clock cycles to execute, due to pipelining, after filling the pipeline, on every clock another instruction finished its execution.

Effectively, the number of instructions executed per second is the same as the clock rate.

| IF              | ID | ΕX | MEM | WB  |     |     |     |    |

|-----------------|----|----|-----|-----|-----|-----|-----|----|

| ļi              | IF | ID | EX  | MEM | WB  |     |     |    |

| $t \rightarrow$ |    | IF | ID  | ΕX  | MEM | WB  |     |    |

|                 |    |    | IF  | ID  | ΕX  | MEM | WB  |    |

|                 |    |    |     | IF  | ID  | ΕX  | MEM | WB |

source: wikimedia.org (CC)

## **LIMITATIONS OF PIPELINING**

• Data Hazard:

if an instruction requires as input a value produced by the previous instruction, this value may not be available at stage 2 (decode and fetch operands) since the previous instruction only saves its results at stage 5.

Solutions: stall the pipeline (instruction must wait for result of previous)

OR use a technique called bypassing to forward the result of the previous instruction at stage 3 of its executionOR reorder instructions to avoid this dependency

• Control Hazard:

a change of control flow (e.g. a branch instruction) causes the pipeline to be flushed, meaning that following instructions that already were fetched and decoded will be discarded.

#### **Consequence:**

the average number of instructions executed per second is lower than the clock rate.

## **COMPARING RISC X CISC**

| RISC                                                                                                                                                      | CISC                                                                                                   |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|

| Instruction set has a reduced number of instructions                                                                                                      | Instruction set has a large number of instructions                                                     |  |  |

| Instructions are very simple                                                                                                                              | Instructions are complex, i.e. have a high semantic content                                            |  |  |

| Large number of general purpose register                                                                                                                  | Small number of registers                                                                              |  |  |

| Instruction codes have fixed size                                                                                                                         | Instructions are coded in a variable number of bytes                                                   |  |  |

| Instruction decoding is very simple and typically performed by a table in ROM                                                                             | Instruction decoding is complex                                                                        |  |  |

| Instruction execution is simple, typically requiring a single clock cycle                                                                                 | Instruction execution is complex and typically uses microprogramming, i.e. interpretation by microcode |  |  |

| Regular execution of the instructions                                                                                                                     | Execution steps varies from instruction to instruction                                                 |  |  |

| Execution time is regular, typically a single clock cycle                                                                                                 | Execution time varies significantly among instructions                                                 |  |  |

| Architecture is prone to the use of a pipeline in the implementations, resulting in N times performance improvement (N is the number of pipeline stages). | Architecture is not prone to the use of Pipeline.                                                      |  |  |

## **COMPARING RISC X CISC**

When the same source program is compiled to a RISC processor and to a CISC processor:

- The number of machine instructions of the compiled program is typically larger on the RISC

- The size of the compiled program (measured in bytes) is typically larger on the RISC

- The performance (inverse of the time to execute the program) is typically better on the RISC

## **COMPARING RISC X CISC**

From a HW perspective, the design of a RISC processor is significantly simpler than that of a CISC:

- Shorter design cycle,

- Lower number of transistors to implement,

- Less area on silicon die.

## **ECONOMICS OF INTEGRATED CIRCUITS MANUFACTURING**

The cost of a chip is determined mainly by:

- Cost of the die (cost of manufacturing a wafer divided by the number of good dies per wafer)

- Testing costs (both for die testing and testing after packaging)

- Packaging costs

- Yield (percentage of functional chips).

## **ECONOMICS OF INTEGRATED CIRCUITS MANUFACTURING**

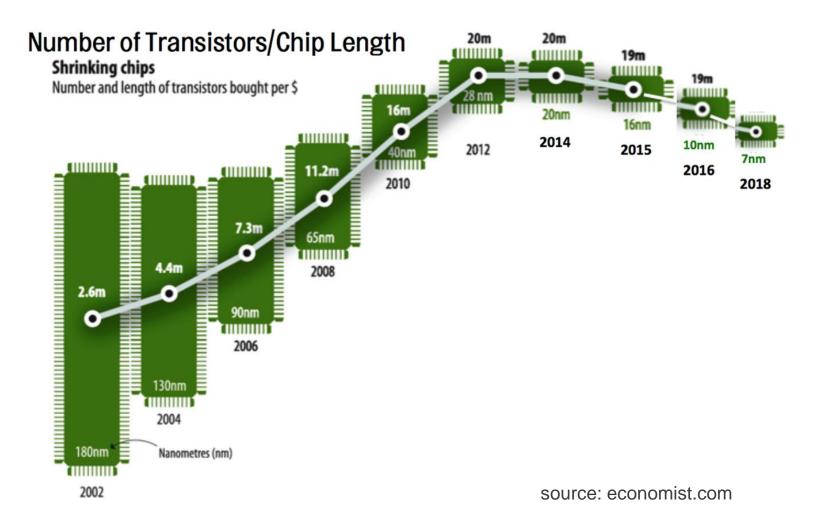

Curve shows how many transistors can be purchased with one dollar for each manufacturing technology over time.

This graph represents the situation in 2018. At the time, the most costeffective technology was 20 nm.

Over time, as the processes mature, transistors cost lowers. Until a given technology enters obsolescence.

## **ECONOMICS OF INTEGRATED CIRCUITS MANUFACTURING**

#### Key design decision:

If currently the "sweet spot" (best value for money) is a given manufacturing technology and a transistor count of T millions transistors, **what is the best use for this asset?**

- 1. CISC core + little Cache/Memory/Peripherals

- 2. RISC core + large amount of Cache/Memory/Peripherals

Most silicon vendors select the second alternative

## **RISC VS CISC TODAY**

Currently, there is a trend to mix the best features of both paradigms. The convergence of RISC and CISC has not been named yet, but the characteristics of novel processors are:

- Large instruction set

- Regular instructions, prone to pipelining

- Pipelines from 3 to 20 stages

- No microcode

#### **RISC VS CISC TODAY**

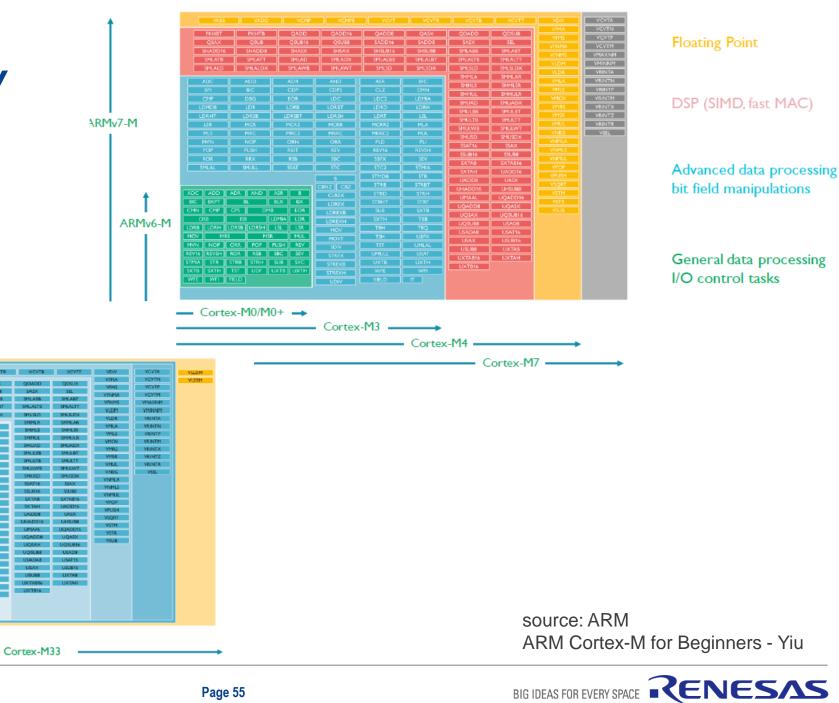

Instruction set of Cortex-M

including Cortex-M23 and

Cortex-M33

ARMv8-M

ARMv8-M Baseline

Cortex-M23

## **3 – ARM CORTEX-M ARCHITECTURE**

- History of ARM

- Cortex-M Features

- Cortex-M Instruction Set Architecture

- Instruction Set

- Memory Access

- Memory-mapped I/O

- Exception Handling

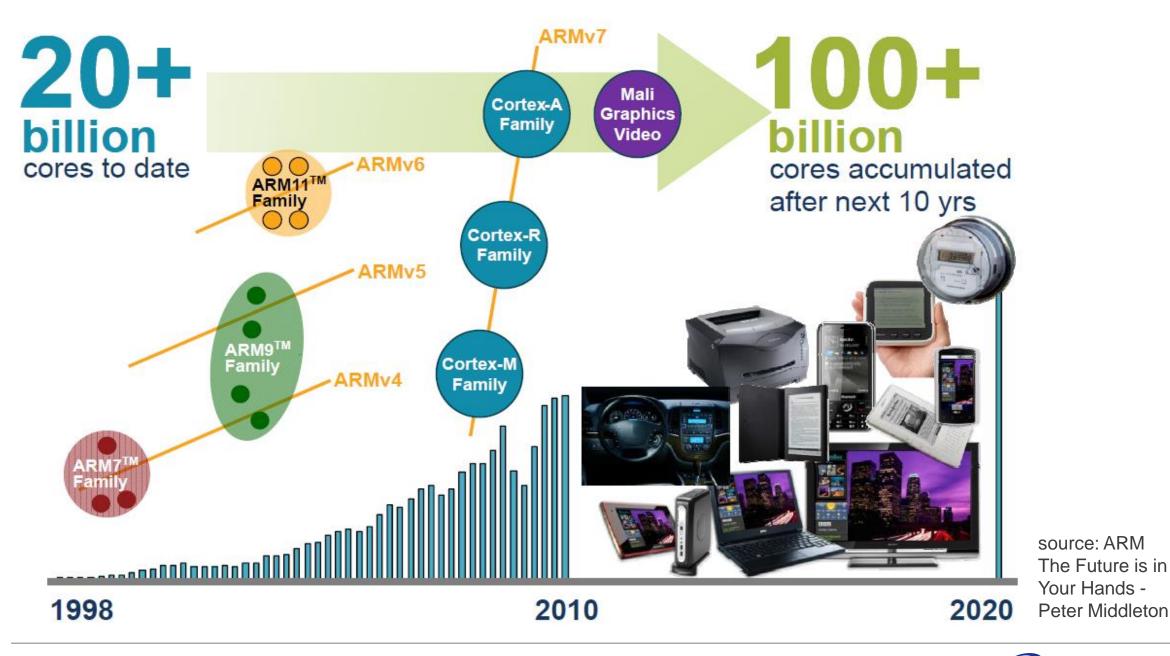

## 3.1 – ARM HISTORY

- Over time, several ARM architecture versions were released. From the seminal ARMv1 to the ARMv8.3-A, released in 2017. The documentation of these standards is available on the arm.com website.

- For each architectural version there are several implementations

© 2020 Renesas Electronics Corporation. All rights reserved.

BIG IDEAS FOR EVERY SPACE RENESAS

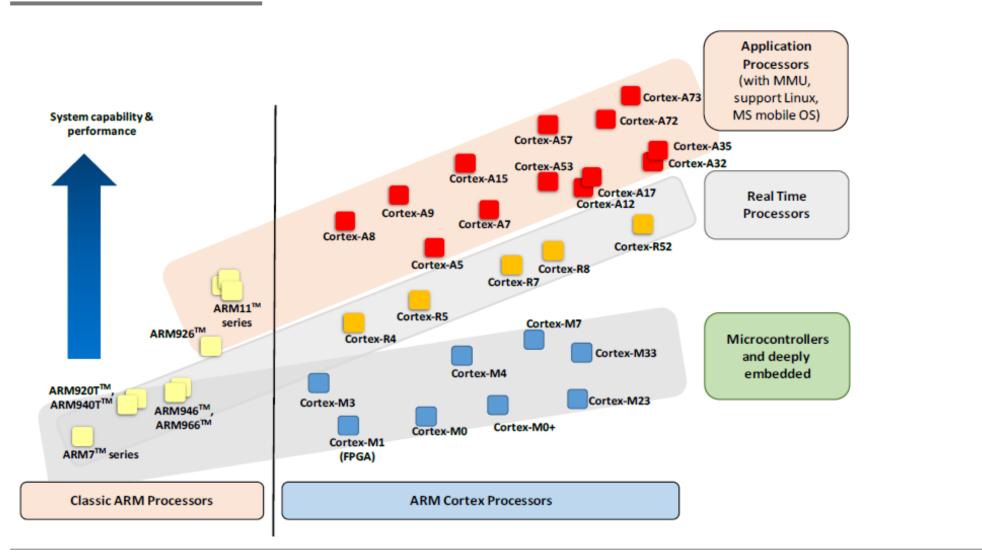

## **ARM PROCESSOR FAMILY**

source: ARM ARM Cortex-M for Beginners - Yiu

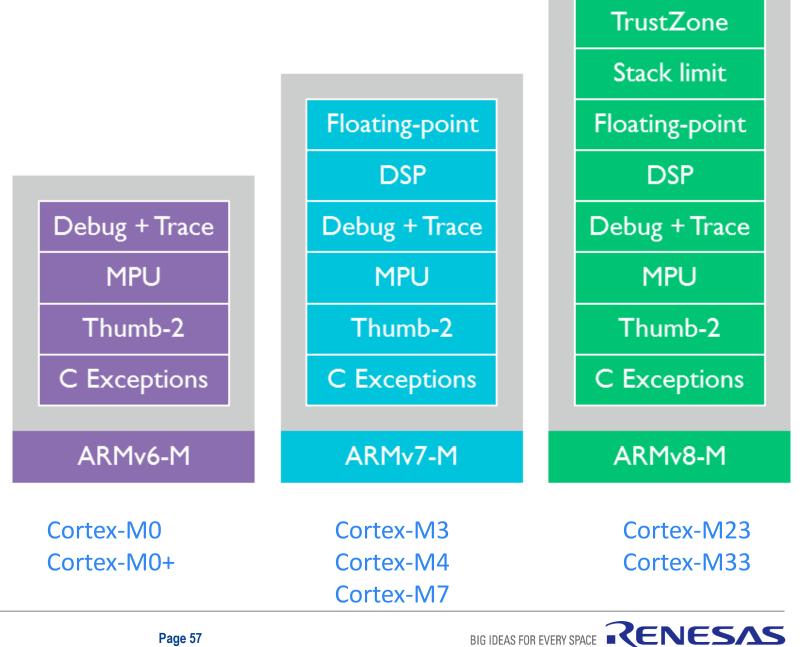

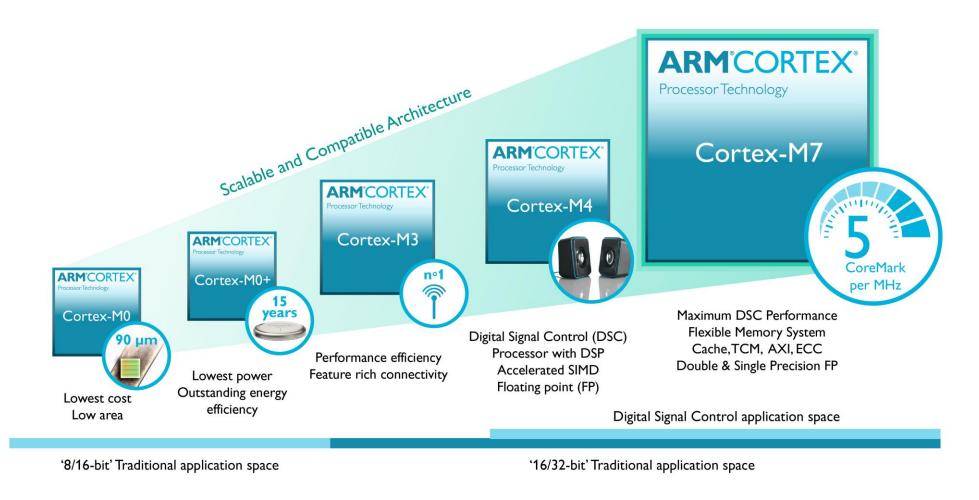

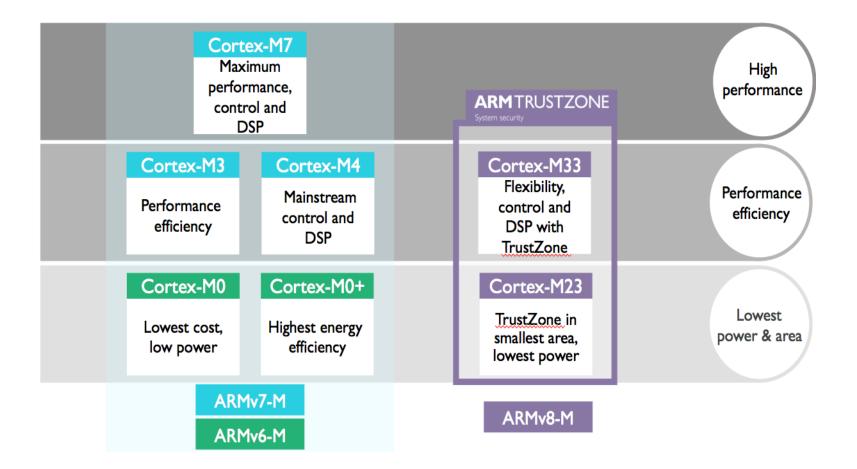

## **THE CORTEX-M FAMILY**

source: community.arm.com

## THE CORTEX-M FAMILY

In 2016, the Cortex-M33 and Cortex-M23 were added to the Cortex-M family.

source: community.arm.com

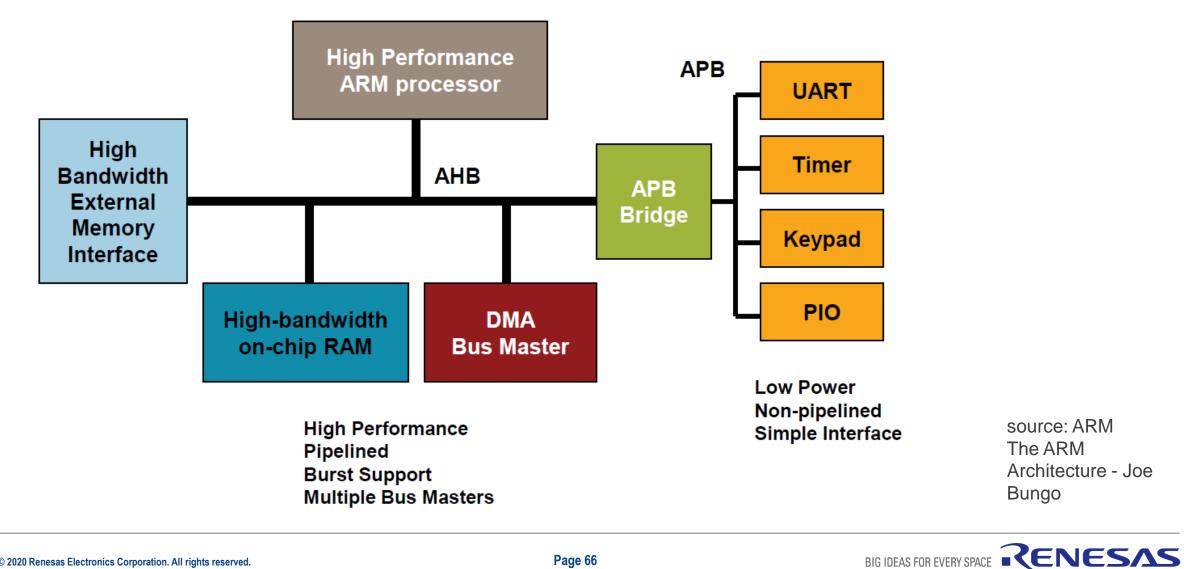

Among the distinguishing features of the Cortex-M architecture are:

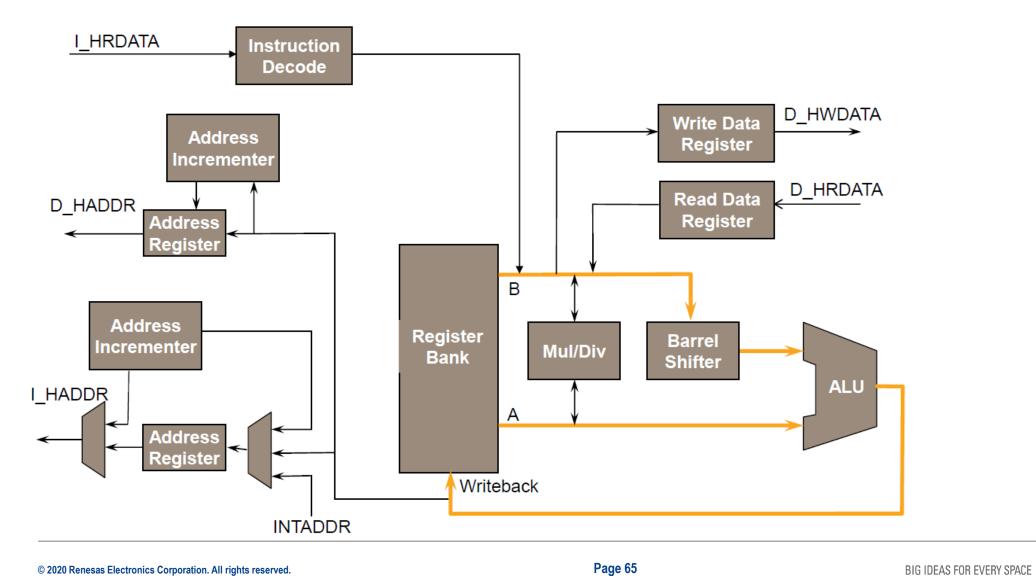

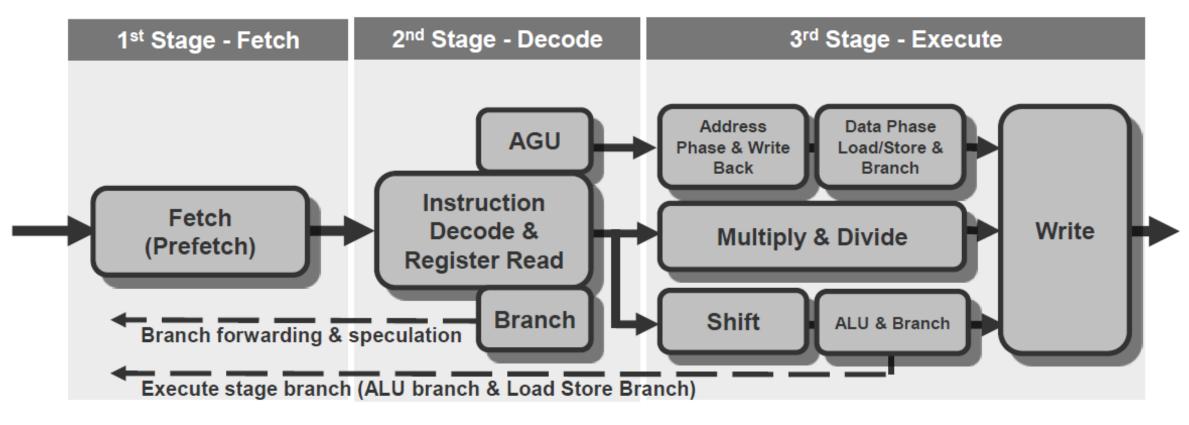

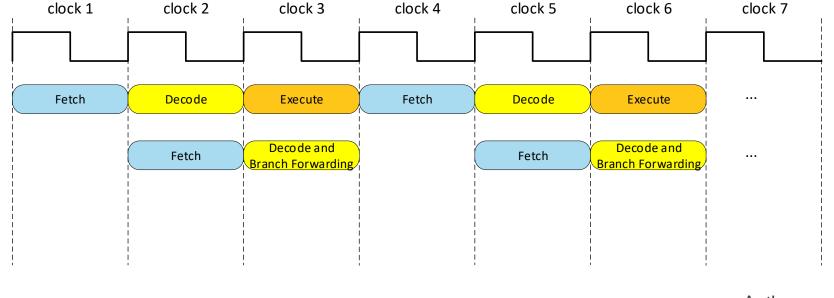

- 3-stage pipeline (except for Cortex-M7): Fetch, Decode, Execute,

- Harvard architecture (except for Cortex-M0 and M0+),

- Designed for power efficiency (includes an ultra low-power deep sleep),

- Thumb-2 instruction set, combining ARM performance and Thumb code density,

- Interrupt Controller (NVIC) is defined in the architecture; low latency vectored interrupt servicing,

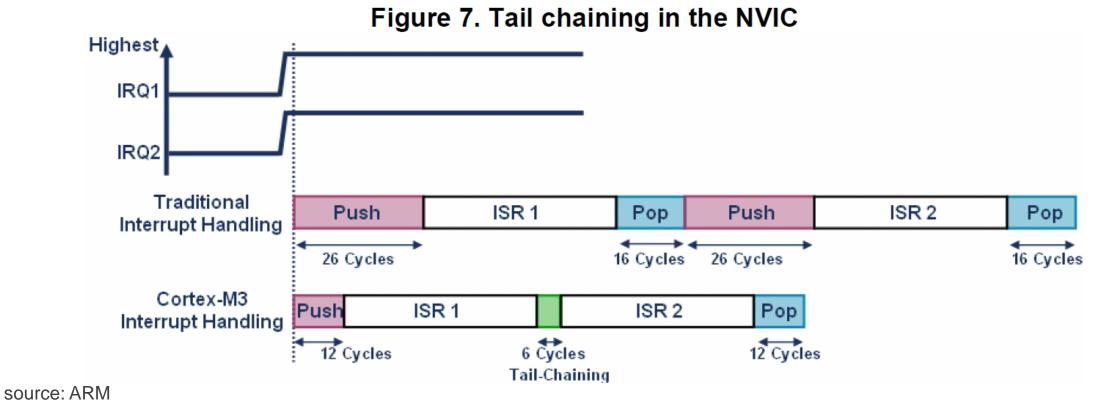

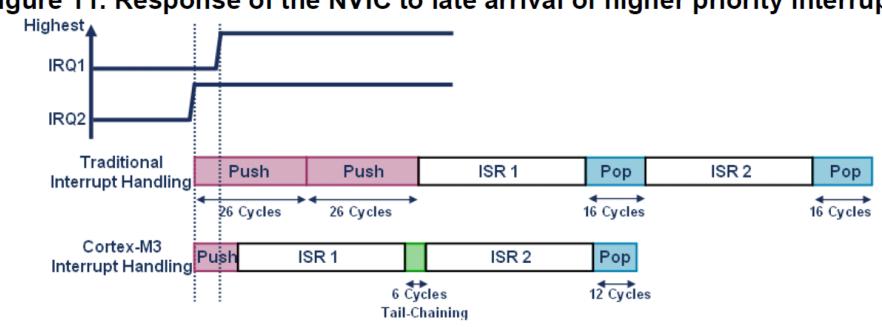

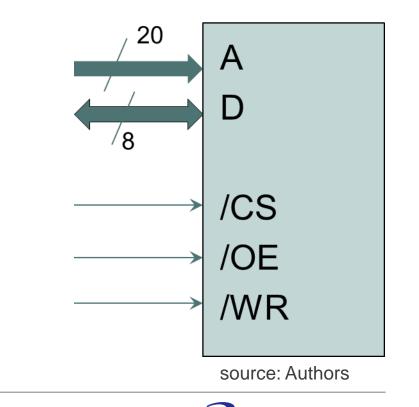

- Interrupt servicing with tail-chaining and late arrival functionalities,

- Bit-banding to provide faster bit operations in memory and memory mapped I/O,

- MPU = Memory Protection Unit,

- Most instructions can be conditional.

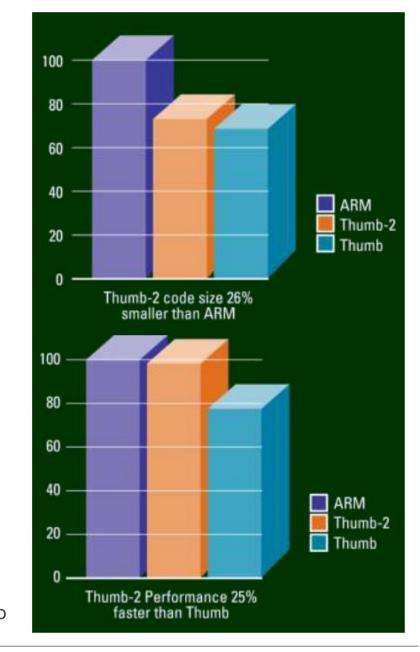

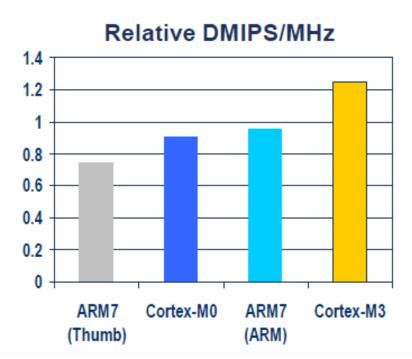

- The ARM7TDMI had two instructions sets:

- ARM with 32-bit instructions, higher performance and lower code density,

- Thumb with 16-bit instructions, lower performance and higher code density.

- Cortex-M has a single instruction set: Thumb-2

- It mixes 16-bit and 32-bit instructions. Its code density is similar to Thumb and its performance is similar to ARM.

**BIG IDEAS FOR EVERY SP**

RENESAS

source: ARM The ARM Architecture - Joe Bungo

| Comparison                   | Cortex-M0  | Cortex-M3   |  |

|------------------------------|------------|-------------|--|

| DMIPS/MHz                    | 0.9        | 1.25        |  |

| Gate count                   | 12k        | 43k         |  |

| Number interrupts            | 1-32 + NMI | 1-240 + NMI |  |

| Interrupt priorities         | 4          | 256         |  |

| Breakpoints, Watchpoints     | 4/2, 2/1   | 8/4, 2/1    |  |

| MPU, integrated trace option | No         | Yes         |  |

| Hardware Divide              | No         | Yes         |  |

source: ARM ARM Cortex-M Processor Family

# **Cortex-M3 Datapath**

source: ARM The ARM Architecture - Joe Bungo

RENESAS

BIG IDEAS FOR EVERY SPACE

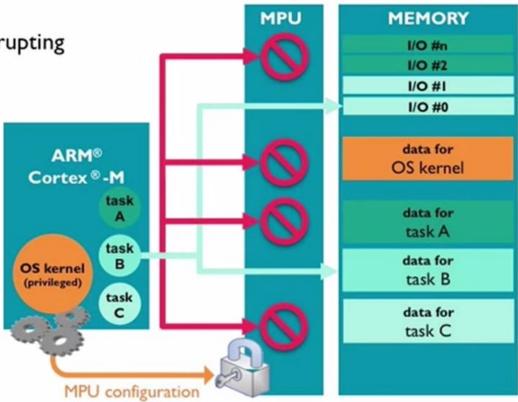

#### Memory Protection Unit (MPU)

- Prevents application task from corrupting OS or other task data

- Improves system reliability

- Configurable regions

- Address

- Size

- Memory attributes

- Access permissions

- Optional in all processors (except Cortex-M0)

source: ARM How to Choose Your ARM Cortex-M Processor - Tim Menasveta

Cortex-M4 Pipeline

source: ARM The ARM Architecture - Joe Bungo

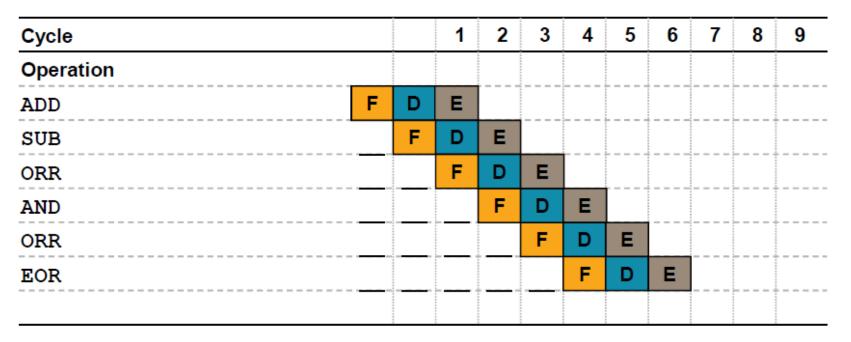

Cortex-M4 Pipeline – example for optimal execution

F-Fetch D-Decode E-Execute

source: ARM ARM Cortex-M3 Introduction - ARM University Relations

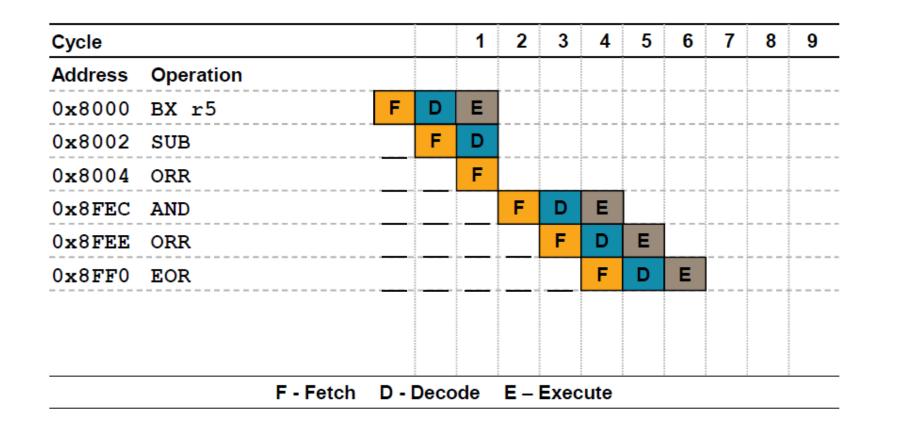

Cortex-M4 Pipeline – pipeline flush due to indirect branch (no forwarding)

source: ARM ARM Cortex-M3 Introduction - ARM University Relations

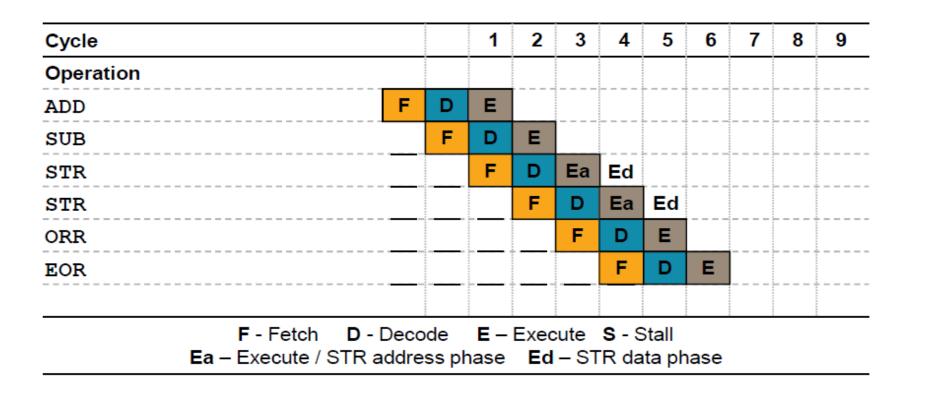

Cortex-M4 Pipeline – Harvard architecture allows for concurrent access to code and data memory.

source: ARM ARM Cortex-M3 Introduction - ARM University Relations

## **3.3 – CORTEX-M4 INSTRUCTION SET ARCHITECTURE**

The Instruction Set Architecture (ISA) presents the Programmer's View of the processor, including:

- Data types

- Processor Modes

- Processor Registers

- Instruction Set

- Memory Accessing

- Exception Processing

The Cortex-M4 instruction set can operate on the following data types:

• **bit:** stores a single bit of information (0 or 1).

Bit banding instructions can set or clear bits in specific memory regions.

- **byte:** 8-bit. Each byte in memory is individually addressable.

- half-word: 16-bit. The address of a half-word in memory is the address of its least significant byte.

- word: 32-bit. The address of a word in memory is the address of its least significant byte.

- double-word: 64-bit. Requires a register pair to be stored, such as R1:R0 (concatenation of R1 and R0 with R1 being the most significant word). The address of a double-word in memory is the address of its least significant byte.

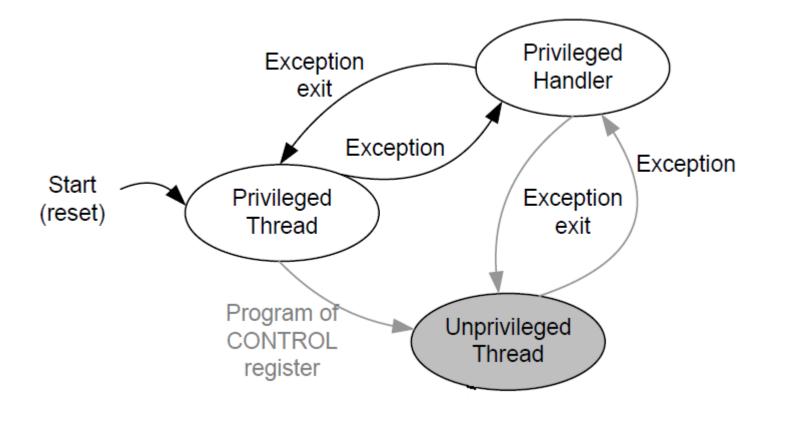

The Cortex-M4 processor modes are:

- Privileged Thread mainly for OS execution

- Unprivileged Thread mainly for Application code

- Privileged Handler -

for exception handling code

Remark: there are two stacks: Main and

Process.

The usage of these stacks is related to the

processor mode.

source: ARM ARM Cortex-M for Beginners - Yiu

The Cortex-M4 has two stacks:

- Main stack addressed by MSP (Main Stack Pointer) mainly to be used by the Operating System (OS) and exception handlers.

- Process stack addressed by PSP (Process Stack Pointer) mainly to be used by the Application threads.

Only one stack is active at any given time, as selected by the CONTROL register. Register R13 (SP) maps to the active stack pointer, either MSP or PSP.

#### Table B1-1 Mode, privilege and stack relationship

| Mode    | Privilege    | Stack pointer | Typical usage model                                                                                                                                                                                                     |                                                            |

|---------|--------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Handler | Privileged   | Main          | Exception handling.                                                                                                                                                                                                     |                                                            |

| Thread  | Privileged   | Main          | Execution of a privileged process or thread using a common stack<br>in a system that only supports privileged access.                                                                                                   |                                                            |

|         |              | Process       | Execution of a privileged process or thread using a stack reserved<br>for that process or thread in a system that only supports privileged<br>access, or that supports a mix of privileged and unprivileged<br>threads. |                                                            |

| Thread  | Unprivileged | Main          | Execution of an unprivileged process or thread using a common stack in a system that supports privileged and unprivileged access.                                                                                       |                                                            |

|         |              | Process       | Execution of an unprivileged process or thread using a stack<br>reserved for that process or thread in a system that supports<br>privileged and unprivileged access.                                                    | source: ARM<br>ARMv7-M<br>Architecture<br>Reference Manual |

Available on the Cortex-M4 with FDI I only

#### 3.3 – CORTEX-M4 ISA – REGISTERS

The register set of the Cortex-M4 consists of:

- General Purpose Registers (R0-R15)

- Floating Point Registers (S0-S31)

- Special Registers (xPSR, PRIMASK, FAULTMASK, BASEPRI, CONTROL)

All registers are 32-bit wide. Not all bits of the Special Registers are implemented.

source: ARM

| General register | s (Floatii                  |

|------------------|-----------------------------|

| R0               | S1                          |

|                  | S3                          |

|                  | S5                          |

| R2               | S7                          |

| R3               | S9                          |

| R4               | <u>S11</u><br>S13           |

|                  | S15                         |

|                  | S17                         |

| R6               | S19                         |

| R7               | S21                         |

| R8               | S23                         |

|                  | S25                         |

| R9               | S27                         |

| R10              | S29                         |

| R11              | S31                         |

| R12              | FPSCR                       |

| R13 (MSP)        | Main Stack Pointer (M       |

| R13 (PSP)        | Process Stack Pointer (     |

| R14              | Link Register (LR)          |

| R15              | Program Counter (PC)        |

| Name             | Functions                   |

| xPSR             | Program Status Regist       |

| PRIMASK          |                             |

| FAULTMASK        | Interrupt Mask<br>Registers |

| BASEPRI          |                             |

| CONTROL          | Control Register            |

| Floatir                                             | ng Point Unit |     |  |  |  |

|-----------------------------------------------------|---------------|-----|--|--|--|

| S1                                                  | SO            | D0  |  |  |  |

| S3                                                  | S2            | D1  |  |  |  |

| S5                                                  | S4            | D2  |  |  |  |

| S7                                                  | S6            | D3  |  |  |  |

| S9                                                  | S8            | D4  |  |  |  |

| S11                                                 | S10           | D5  |  |  |  |

| S13                                                 | S12           | D6  |  |  |  |

| S15                                                 | S14           | D7  |  |  |  |

| S17                                                 | S16           | D8  |  |  |  |

| S19                                                 | S18           | D9  |  |  |  |

| S21                                                 | S20           | D10 |  |  |  |

| S23                                                 | S22           | D11 |  |  |  |

| S25                                                 | S24           | D12 |  |  |  |

| S27                                                 | S26           | D13 |  |  |  |

| S29                                                 | S28           | D14 |  |  |  |

| S31                                                 | S30           | D15 |  |  |  |

| FPSCR Floating Point Status<br>and Control Register |               |     |  |  |  |

| P)<br>P)        | Main Stack Pointer (MSP),<br>Process Stack Pointer (PSP) |                      |

|-----------------|----------------------------------------------------------|----------------------|

|                 | Link Register (LR)                                       |                      |

|                 | Program Counter (PC)                                     |                      |

|                 | Functions                                                |                      |

|                 | Program Status Registers                                 |                      |

| SK<br>ASK<br>RI | Interrupt Mask<br>Registers                              | Special<br>Registers |

| OL              | Control Register                                         |                      |

ARM Cortex-M for Beginners - Yiu

General Purpose Registers:

- 32-bit wide

- Low registers: R0 .. R7

- High registers: R8 .. R15

- Special usage:

R13 or SP is the Stack Pointer - points to the top of the stack

R14 or LR is the Link Register - stores the procedure return address

R15 or PC is the Program Counter - stores the address of the next instruction fetch

| b31 | b30 | b29 | b28 | b27 | b26 | b25 | b24 | b23 | b22 | b21 | b20 | b19 | b18 | b17 | b16 | b15 | b14 | b13 | b12 | b11 | b10 | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

|     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    |

RENESAS

**BIG IDEAS FOR EVERY SP**

General Purpose Registers:

- the general-purpose registers are accessible by most instructions;

- b0 is the Least Significant Bit (LSb) and b31 is the Most Significant Bit (MSb);

- a register can hold an unsigned integer with values from 0 to 4,294,967,295

or a signed integer with values from -2,147,483,648 to 2,147,483,647;

- when using hexadecimal notation, a 32-bit register holds 8 hex digits. E.g. 0x1234 5678;

- Cortex-M architecture uses 32-bit memory addresses, hence, a single general-purpose register can hold a memory address.

| b31 | b30 | b29 | b28 | b27 | b26 | b25 | b24 | b23 | b22 | b21 | b20 | b19 | b18 | b17 | b16 | b15 | b14 | b13 | b12 | b11 | b10 | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

|     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    |

RENESAS

**BIG IDEAS FOR EVERY SPACE**

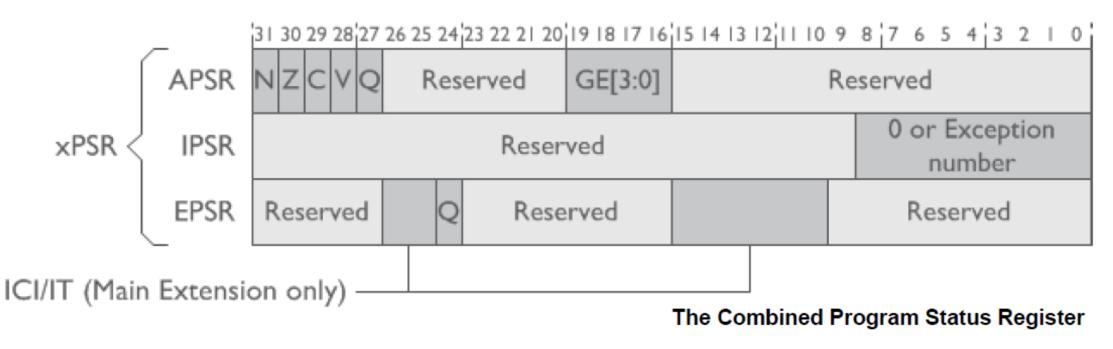

Special Purpose Registers - XPSR

• The three registers APSR, IPSR and EPSR can be accessed individually or combined as XPSR.

### 3.3 – CORTEX-M4 ISA – APSR

#### **APSR = Application Program Status Register**

| 31 | 30 | 29 | 28 | 27 | 26   | 20   | 19       16 | 15 |         |    | 0 |

|----|----|----|----|----|------|------|-------------|----|---------|----|---|

| N  | z  | С  | V  | Q  | Rese | rved | GE[3:0]     |    | Reserve | ed |   |

| Flag | bit   | Description                                                                                                                                      |

|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Ν    | 31    | Negative. For two's complement results this bit is set to indicate that the result is negative.                                                  |

| Z    | 30    | Zero. This bit is set when the result is zero. After a comparison, this bit is set to indicate that the compared values are equal.               |

| С    | 29    | Carry. Set to indicate that the result of an unsigned addition produced overflow. Also set to indicate that un unsigned subtraction underflowed. |

| V    | 28    | Overflow. Set to indicate overflow in a signed arithmetic operation.                                                                             |

| Q    | 27    | Saturation bit. For DSP extension instructions.                                                                                                  |

| GE   | 19:16 | Greater than or Equal. For SIMD instructions.                                                                                                    |

|      |       |                                                                                                                                                  |

#### 3.3 – CORTEX-M4 ISA – IPSR

#### **IPSR = Interrupt Program Status Register**

| IPSR |  | 0 or Exception Number |

|------|--|-----------------------|

|------|--|-----------------------|

| Field               | bit | Description                                                                                                                                                                                                                                                          |

|---------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Exception<br>Number | 8:0 | This field identifies the exception that is currently active (being serviced). The value 0 indicates that no exception is currently active.<br>If this value is non-zero the processor is in Handler mode.<br>If this value is zero the processor is in Thread mode. |

#### 3.3 – CORTEX-M4 ISA – EPSR

#### **EPSR = Execution Program Status Register**

| EPSR | ICI/IT T | ICI/IT |  |

|------|----------|--------|--|

|------|----------|--------|--|

| Field  | bit            | Description                                                                                                                                                                                                                                       |

|--------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Т      | 24             | Thumb. This bit is set to indicate that the instruction set in use is Thumb.<br>On Cortex-M this bit must be set all the time or an exception occurs.<br>On ARM7TDMI, Cortex-R and Cortex-A this bit is 0 when the ARM instruction set is in use. |

| ICI/IT | 26:25<br>15:10 | ICI - used for a interrupted exception-continuable multi-cycle load or store.<br>IT - provide context information for instructions in an IT block.                                                                                                |

#### 3.3 – CORTEX-M4 ISA – XPSR

Mnemonics used to combine the XPSR component registers:

| Mnemonic Registers accesse |                          |

|----------------------------|--------------------------|

| IAPSR                      | IPSR and APSR            |

| EAPSR                      | EPSR and APSR            |

| XPSR                       | All three xPSR registers |

| IEPSR                      | IPSR and EPSR            |

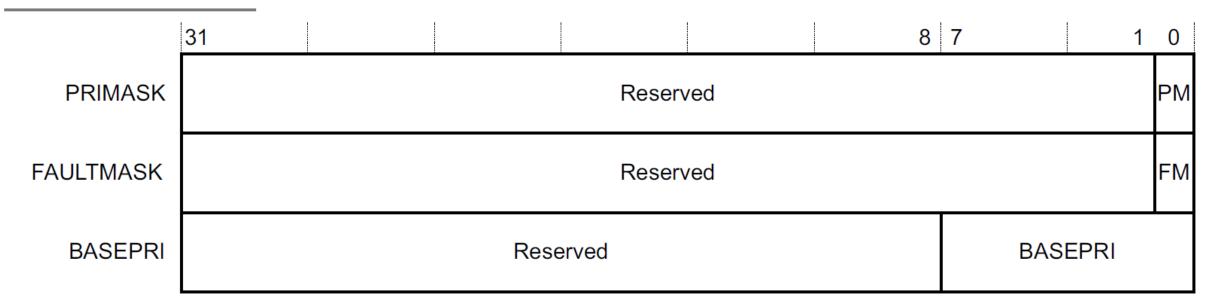

#### 3.3 – CORTEX-M4 ISA – SPECIAL REGISTERS

| Field       | bit          | Description                                                                                                                               |

|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| PM          | PRIMASK[0]   | Set to mask exceptions with configurable priority (priority 0 and lower). Reset to unmask.                                                |

| FM          | FAULTMASK[0] | Set to mask the HardFault exceptions and the configurable priorities (prio -1 and lower).                                                 |

| BASE<br>PRI | BASEPRI[7:0] | Changes the priority level required for exception preemption. Affects only the currently executing code with lower priority than BASEPRI. |

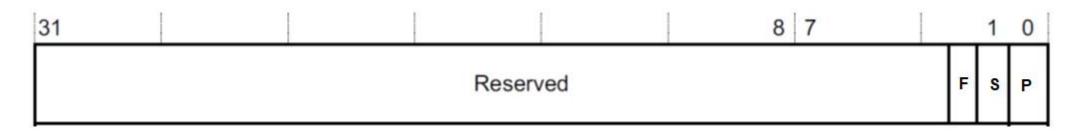

### 3.3 – CORTEX-M4 ISA – CONTROL REGISTER

CONTROL Register

| Field      | bit | Description                                                                                                                                                   |

|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nPRIV      | 0   | When the processor is in Thread mode. 0 = privileged mode; 1 = unprivileged mode.                                                                             |

| SPSEL      | 1   | Stack selection. 0 = use MSP (Main Stack); 1 = use PSP (Process Stack).<br>In Handler mode this bit is always 0.                                              |

| FPCA       | 2   | Implemented only when floating point is available.<br>0 = do not save floating point registers on exception;<br>1 = save floating point context on exception. |

| Source: AF |     |                                                                                                                                                               |

Floating Point Registers:

- The Cortex-M4 with optional floating-point extension, implements 32 32-bit floating point registers named S0 to S31.

- These can be combined two by two forming 16 double precision (64-bit) floating point registers named D0 to D15. D0 is formed by S1:S0 (the concatenation of the registers S1 and S0 where S1 is the most significant word, i.e. the leftmost word).

Before presenting the instruction set, lets examine:

- Assembly syntax

- 3-operand instructions

- Conditional instructions

- Instructions that affect the flags

The most common instruction formats are: (format)

| label:  | MNEMONIC   | Destination, Operand1, Operand2 | ;comment |

|---------|------------|---------------------------------|----------|

| label:  | MNEMONIC   | Destination, Operand2           | ;comment |

| Example | S:         |                                 |          |

| fmtl: A | ADD R2, R4 | , R5 ; R2 = R4 + R5             |          |

; R2 = R2 + R4

fmt2: ADD R2, R4

Suggested assembly source file layout:

$\begin{array}{cccc} \text{col 1} & \text{col 5} & \text{col 13} \\ \downarrow & \downarrow & \downarrow \\ \text{fmt1: ADD} & \text{R2, R4, R5} & ; \text{R2} = \text{R4} + \text{R5} \end{array}$

By setting the TABs to 4 spaces, these positions can be easily obtainable.

Only labels should begin on column 1.

Only mnemonics are compulsory. Labels, operands and comments are optional, although they are all very frequent.

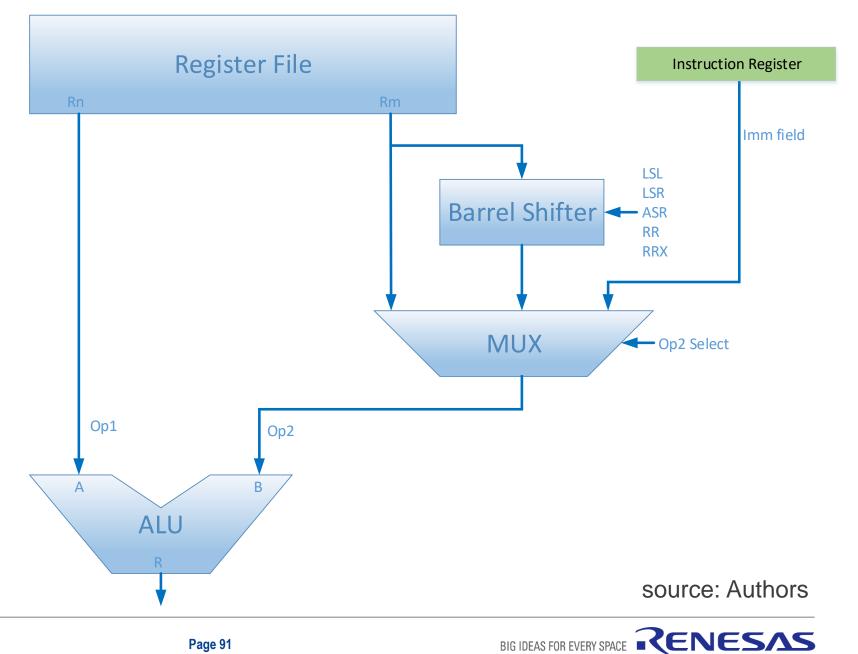

For an instruction with two operands, the first operand (Op1) is always a register. The second operand (Op2) may be a register, or a register that had its contents shifted or rotated, or an immediate value coded in the instruction.

Examples of Operand 2

| ADD | R2, R4, R5        | ;Operand 2 is a register (R5)                                                                                        |

|-----|-------------------|----------------------------------------------------------------------------------------------------------------------|

| ADD | R2, R4, R5,LSL #2 | ;Operand 2 is a shifted register<br>;R5 is shifted left by 2 bits<br>;this corresponds to multiplying its value by 4 |

| ADD | R2, R4, #0xFF     | ;Operand 2 is an immediate value<br>;the hexadecimal value 0xFF                                                      |

In the Cortex-M4 instruction set, the programmer explicitly controls if the result of an instruction should affect the flags: N,Z,C,V.

Most instructions have a variant with the letter S appended to the mnemonic. The S variant means: "set the flags".

| ADD R2, R4, R5  | ;the result of this addition does |  |

|-----------------|-----------------------------------|--|

|                 | ;not affect the flags.            |  |

| ADDS R2, R4, R5 | ;the result of this addition      |  |

|                 | ;affects the N,Z,C and V flags.   |  |

Many Cortex-M4 instruction can be **conditional**, meaning that the instruction only executes if the flags are in a given state. Except for branch instructions, an instruction must be in an IT block to be conditional. The condition is specified by two letters appended after the mnemonic (see condition table on next slide).

| ADD    | R2,R4,R5 | ;the result of this addition does              |

|--------|----------|------------------------------------------------|

|        |          | ;not affect the flags.                         |

| ADDS   | R2,R4,R5 | ;the result of this addition                   |

|        |          | ;affects the N,Z,C and V flags.                |

| ITT    | ΕQ       | ;start of an IT block with 2 instructions      |

| ADDEQ  | R2,R4,R5 | ;if Z is set, execute the ADD                  |

| ADDSEQ | R2,R4,R5 | ;if Z is set, execute the ADD and change       |

|        |          | ;flags according to result of this instruction |

Condition codes mnemonics suffixes

| - | Suffix   | Flags              | Meaning                                                  |

|---|----------|--------------------|----------------------------------------------------------|

|   | EQ       | Z = 1              | Equal                                                    |

|   | NE       | Z = 0              | Not equal                                                |

|   | CS or HS | C = 1              | Higher or same, unsigned                                 |

|   | CC or LO | C = 0              | Lower, unsigned                                          |

|   | MI       | N = 1              | Negative                                                 |

|   | PL       | N = 0              | Positive or zero                                         |

|   | VS       | V = 1              | Overflow                                                 |

|   | VC       | V = 0              | No overflow                                              |

|   | HI       | C = 1 and Z = 0    | Higher, unsigned                                         |

|   | LS       | C = 0 or Z = 1     | Lower or same, unsigned                                  |

|   | GE       | N = V              | Greater than or equal, signed                            |

|   | LT       | N != V             | Less than, signed                                        |

|   | GT       | Z = 0 and $N = V$  | Greater than, signed                                     |

|   | LE       | Z = 1 and N != V   | Less than or equal, signed                               |

|   | AL       | Can have any value | Always. This is the default when no suffix is specified. |

BIG IDEAS FOR EVERY SPACE RENESAS

Code examples for conditional instructions.

| cmp   | R12,R10    | ;compare the unsigned values in R12 and R10, change flags |

|-------|------------|-----------------------------------------------------------|

| beq   | opl        | ;branch to op1 if the values of R12 and R10 are equal     |

| ite   | hi         | ;two-instruction IT block with HI condition               |

| addhi | R12,R12,#1 | ;if R12 > R10 then increment R12                          |

| addls | R10,R10,#1 | ;else increment R10                                       |

|       |            |                                                           |

op1:

• • •

An immediate value is a constant whose value is encoded in the instruction. Hence, a limited range of values is allowed.

The notation for immediate values is #value.

The notation for negative values is #-15.

The notation for hexadecimal values is #0xFA0.

Example:

ADD  $R_{2}, R_{4}, \#_{5}$ ;  $R_{2} = R_{4} + 5$

- Cortex-M4 instruction codes are either 16-bit or 32-bit.

- 16-bit instructions are called narrow and may have a .N suffix.

- 32-bit instructions are called wide and may have a .W suffix.

- Some mnemonics may be coded either in narrow or wide format, for example:

| 0x37a: | 0x1840        | ADDS.N | RO, RO, R1 | //16-bit code |

|--------|---------------|--------|------------|---------------|

| 0x37c: | 0xeb10 0x0001 | ADDS.W | R0, R0, R1 | //32-bit code |

- 16-bit and 32-bit instruction code can be freely intermixed in a program.

- All instructions must be halfword aligned, i.e. must be stored on an even address.

- Hence, PC will never hold an odd address => bit 0 of PC is always 0.

- When writing a 32-bit value to PC, bit 0 is ignored => can be used for other purpose.

- In other ARM processors, use bit 0 for interworking (i.e. change of instruction set).

- On Cortex-M, bit 0 must be a 1. This value is stored to the T flag in XPSR.

- Instructions that can be used for interworking (i.e. write to T flag):

- BX

- BLX

- pop {PC}

- Instructions that have as destination register the PC, cause a branch

- MOV PC, LR

- ADD PC, PC,R1

- There are restrictions on which instructions may write to PC.

#### **Arithmetic instructions**

| Instruction              | Description                                                              | Action                                  |

|--------------------------|--------------------------------------------------------------------------|-----------------------------------------|

| ADD Rd, Rn, Op2          | Add a register to Operand2                                               | Rd = Rn + Op2                           |

| ADC Rd, Rn, Op2          | Add a register to Operand2 and to Carry                                  | Rd = Rn + Op2 + CY                      |

| SUB Rd, Rn, Op2          | Subtract from a register the Operand2                                    | Rd = Rn - Op2                           |

| SBC Rd, Rn, Op2          | Subtract from a register the Operand2 and the Borrow (negation of Carry) | Rd = Rn - Op2 - /CY                     |

| RSB Rd, Rn, Op2          | Subtract from Operand2 a register                                        | Rd = Op2 - Rn                           |

| RSC Rd, Rn, Op2          | Subtract from Operand2 a register and the Borrow                         | Rd = Op2 - Rn - /CY                     |

| MOV Rd, Op2              | Move to Rd from Operand2 (put a copy of Operand2 into Rd)                | Rd = Op2                                |

| MVN Rd, Op2              | Move to Rd /Operand2                                                     | Rd = /Op2                               |

| MOVT Rd, <imm16></imm16> | Move to Rd[31:16] from imm16. Lower bits of Rd are unaffected            | Rd[31:16] = imm16<br>Rd[15:0] unchanged |

BIG IDEAS FOR EVERY SPACE RENESAS

#### **Compare and Test**

| Instruction | Description                                                          |  |

|-------------|----------------------------------------------------------------------|--|

| CMP Rn, Op2 | Compare: Subtract from Rn the Operand2, discard result, change flags |  |

| CMN Rn, Op2 | Compare negative: Add Rn to Operand2, discard result, change flags   |  |

| TST Rn, Op2 | Test: Rn AND Operand2, discard result, change flags                  |  |

| TEQ Rn, Op2 | Test equivalence: Rn EOR Operand2, discard result, change flags      |  |

|             |                                                                      |  |

|             |                                                                      |  |

|             |                                                                      |  |

|             |                                                                      |  |

|             |                                                                      |  |

#### Logical

| Instruction     | Description                                              | Action          |

|-----------------|----------------------------------------------------------|-----------------|

| AND Rd, Rn, Op2 | AND: bitwise logical AND a register to Operand2          | Rd = Rn AND Op2 |

| ORR Rd, Rn, Op2 | OR: bitwise logical OR a register to Operand2            | Rd = Rn OR Op2  |

| EOR Rd, Rn, Op2 | Exclusive OR: bitwise logical XOR a register to Operand2 | Rd = Rn XOR Op2 |

| ORN Rd, Rn, Op2 | OR NOT: bitwise logical OR a register to NOT(Operand2)   | Rd = Rn OR /Op2 |

|                 |                                                          |                 |

|                 |                                                          |                 |

|                 |                                                          |                 |

|                 |                                                          |                 |

|                 |                                                          |                 |

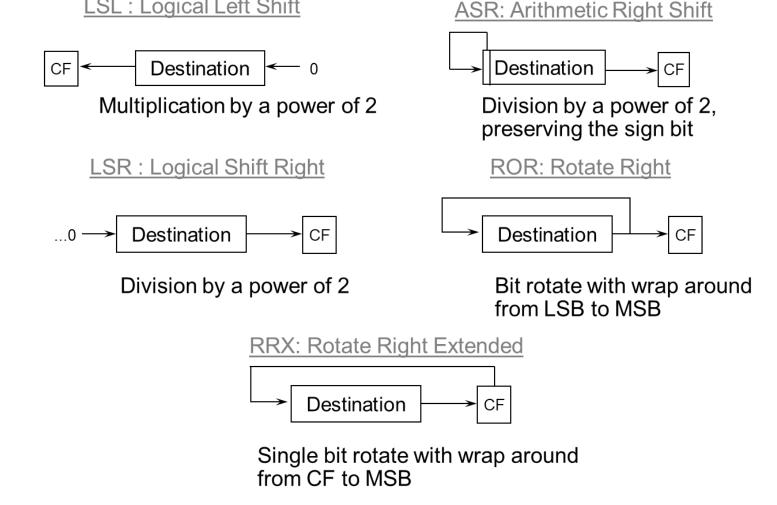

#### **Shift Instructions**

| Instruction          | Description                                            | #imm Sh range |

|----------------------|--------------------------------------------------------|---------------|

| ASR Rd, Rn, Sh       | Arithmetic Shift Right (preserves signal)              | 132           |

| LSL Rd, Rn, Sh       | Logical Shift Left                                     | 031           |

| LSR Rd, Rn, Sh       | Logical Shift Right                                    | 132           |

| ROR Rd, Rn, Sh       | Rotate Right                                           | 031           |

| RRX Rd, Rn           | Rotate Right Extended                                  |               |

|                      |                                                        |               |

| Remark: Sh is either | the lower 8 bits of a register (value from 0255)       |               |

|                      | a 5-bit immediate value representing either 132 or 031 |               |

|                      |                                                        |               |

BIG IDEAS FOR EVERY SPACE RENESAS

LSL : Logical Left Shift

RENESAS

BIG IDEAS FOR EVERY SPACE

source: ARM The ARM Architecture

#### Shift Operators to be used in Operand2

| Operator             | Description                                            | #imm Sh range |

|----------------------|--------------------------------------------------------|---------------|

| ASR Sh               | Arithmetic Shift Right (preserves signal)              | 132           |

| LSL Sh               | Logical Shift Left                                     | 031           |

| LSR Sh               | Logical Shift Right                                    | 132           |

| ROR Sh               | Rotate Right                                           | 031           |

| RRX                  | Rotate Right Extended                                  |               |

|                      |                                                        |               |

| Remark: Sh is either | the lower 8 bits of a register (value from 0255)       |               |

|                      | a 5-bit immediate value representing either 132 or 031 |               |

| Usage:               | R4, LSL #3 (Operand2 is R4 << 3)                       |               |

Multiply

| Instruction                                                                                                                 | Description                                  | Action                                     |  |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------|--|

| Instructions that multiply 32-bit by 32-bit resulting 32-bit with wrapping (LSW is preserved and higher bits are discarded) |                                              |                                            |  |

| MUL Rd, Rm, Rs                                                                                                              | Multiply                                     | Rd = Rm * Rs                               |  |

| MLA Rd, Rm, Rs, Rn                                                                                                          | Multiply and accumulate                      | Rd = Rm * Rs + Rn                          |  |

| MLS Rd, Rm, Rs, Rn                                                                                                          | Multiply and subtract                        | Rd = Rm * Rs - Rn                          |  |

| Long multiplication: multiply 32-bit by 32-bit resulting 64-bit                                                             |                                              |                                            |  |

| UMULL RdLo, RdHi, Rm, Rs                                                                                                    | Unsigned long multiply                       | RdHi:RdLo = unsigned(Rm*Rs)                |  |

| UMLAL RdLo, RdHi, Rm, Rs                                                                                                    | Unsigned long multiply and accumulate        | RdHi:RdLo = unsigned(RdHi:RdLo +<br>Rm*Rs) |  |

| UMAAL RdLo, RdHi, Rm, Rs                                                                                                    | Unsigned long multiply and accumulate double | RdHi:RdLo = unsigned(RdHi+RdLo +<br>Rm*Rs) |  |

| SMULL RdLo, RdHi, Rm, Rs                                                                                                    | Signed long multiply                         | RdHi:RdLo = signed(Rm*Rs)                  |  |

| SMLAL RdLo, RdHi, Rm, Rs                                                                                                    | Signed long multiply and accumulate          | RdHi:RdLo = signed(RdHi:RdLo + Rm*Rs)      |  |

| © 2020 Renesas Electronics Corporation. All rights reserved.                                                                | Page 106                                     | BIG IDEAS FOR EVERY SPACE RENESAS          |  |

#### Divide

| Instruction     | Description     | Action       |

|-----------------|-----------------|--------------|

| UDIV Rd, Rn, Rm | Unsigned divide | Rd = Rn / Rm |

| SDIV Rd, Rn, Rm | Signed divide   | Rd = Rn / Rm |

Bit field operations

A bit field is a sequence of bits in a register.

- A bit field is characterized by two values:

- Width: the number of bits in the bit field (1..32);

- Isb: the position of the least significant bit in the bitfield (0..31).

| Instruction                                   | Description                                                | Action                                              |

|-----------------------------------------------|------------------------------------------------------------|-----------------------------------------------------|

| BFC Rd,# <lsb>,#<width></width></lsb>         | Bit field clear                                            | clear Rd[(width+lsb-1)lsb], others unchanged        |

| BFI Rd, Rn,# <lsb>,#<width></width></lsb>     | Bit field insert. Copy the <width> LSb of Rn to Rd</width> | Rd[(width+lsb-1)lsb] = Rn[(width-1)0]               |

| SBFX Rd,<br>Rn,# <lsb>,#<width></width></lsb> | Signed bit field extract.                                  | Copy bitfield from Rn to LSb of Rd and sign extend. |

| UBFX Rd,<br>Rn,# <lsb>,#<width></width></lsb> | Unsigned bit field extract.                                | Copy bitfield from Rn to LSb of Rd and zero extend. |

RENESAS

**BIG IDEAS FOR EVERY SPACE**

Memory access instructions

| Instruction type | Description                                                                                  |

|------------------|----------------------------------------------------------------------------------------------|

| LDRB             | Load byte. Read a byte from memory and store in the LSB of a register.                       |

| LDRH             | Load half word. Read a half-word from memory and store in the lower half-word of a register. |

| LDR              | Load register. Read a word from memory and store in a register.                              |

| LDRD             | Load double. Read a double word form memory and store in two registers.                      |

| STRB             | Store byte. Store the LSB of a register into memory.                                         |

| STRH             | Store half-word. Store the lower half of a register into memory.                             |

| STR              | Store register. Store a register into memory.                                                |

| STRD             | Store double. Store the two registers into memory.                                           |

| LDM              | Load multiple. Read several (up to 16) registers from memory.                                |

| STM              | Store multiple. Store several (up to 16) registers into memory.                              |

Memory access instructions – addressing

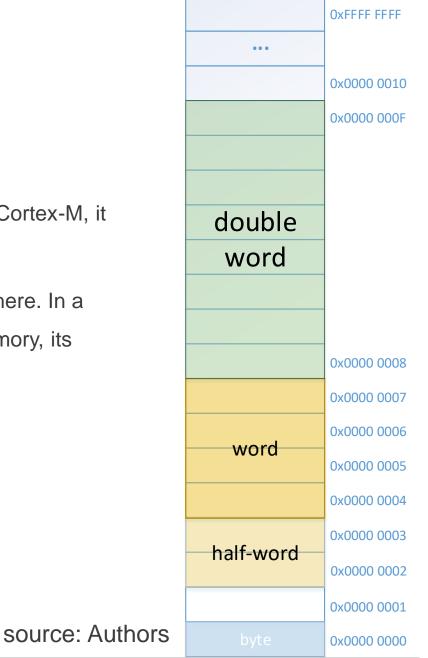

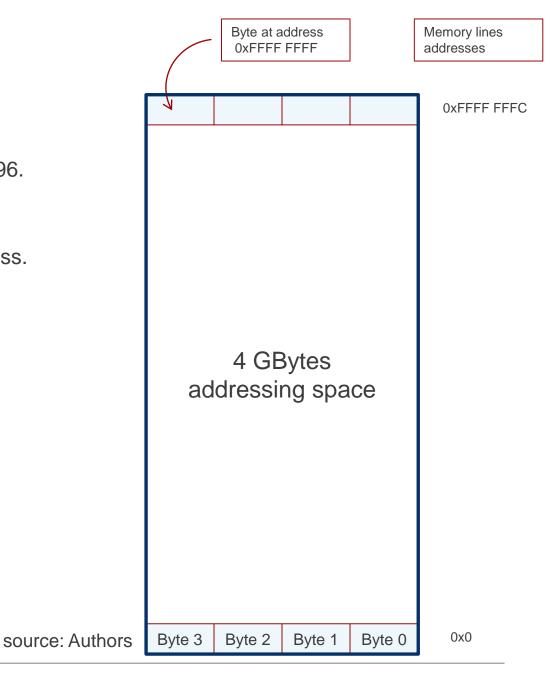

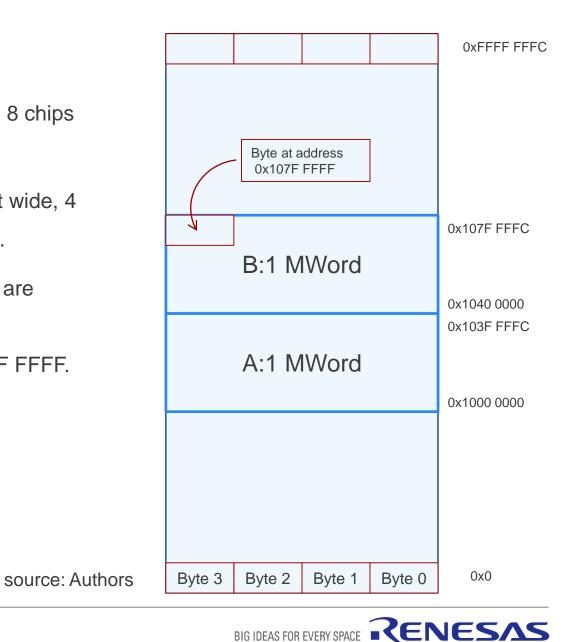

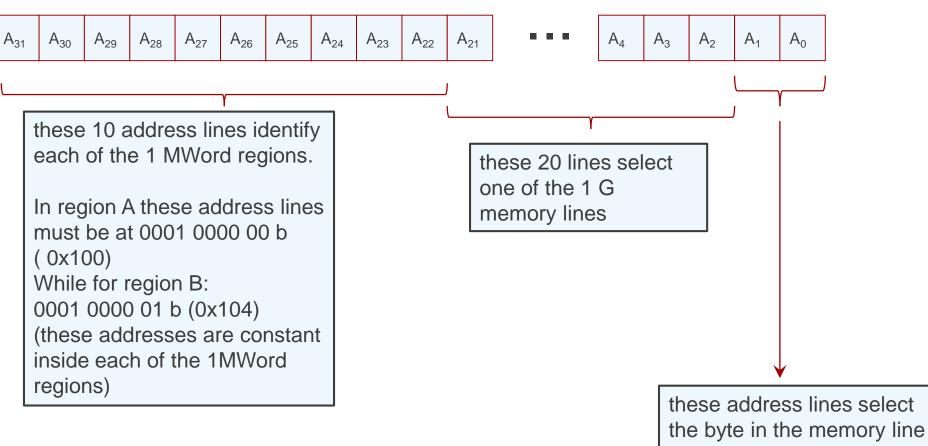

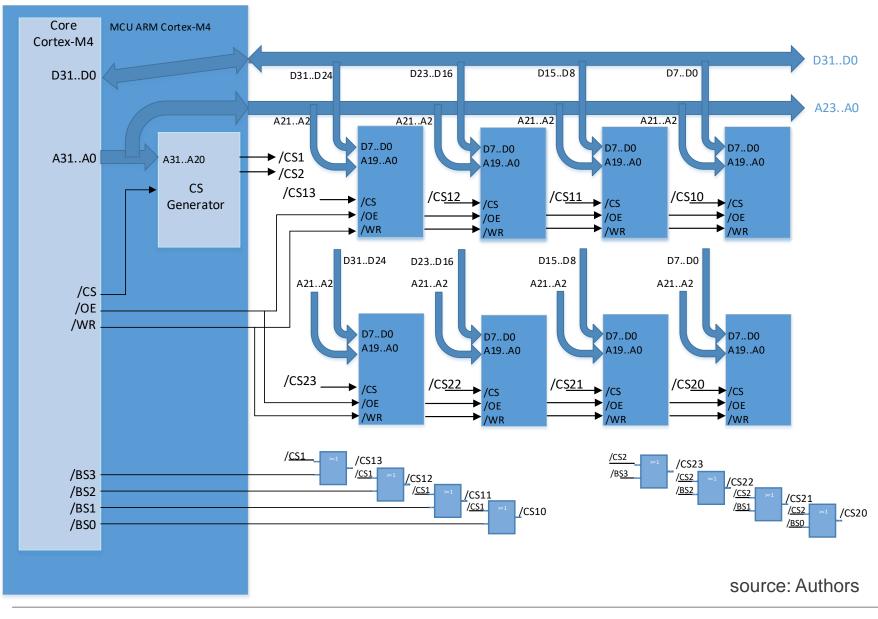

For the purposes of addressing, memory is just a very large vector of bytes. For Cortex-M, it is a vector with 4G entries.

The four data types that can be accesses with LDR/STR instructions are shown here. In a little-endian memory system, when a data type occupies more than 1 byte in memory, its address is the address of the LSB (Least Significant Byte).

shown: byte at 0x0, half-word at 0x2, word at 0x4, and double-word at 0x8

RENESAS

BIG IDEAS FOR EVERY SPACE

|                      | 31          | 24          | 23          | 16          | 15        |         | 8     | 7         |           | 0 |

|----------------------|-------------|-------------|-------------|-------------|-----------|---------|-------|-----------|-----------|---|

| Word at<br>Address A | Byte at add | dress (A+3) | Byte at ado | dress (A+2) | Byte at a | address | (A+1) | Byte at a | address A |   |

|                      |             |             | Halfword at | Address A   | Byte at a | address | (A+1) | Byte at a | address A |   |

#### Figure A3-1 Little-endian byte format

|                      | 31        | 24        | 23          | 16          | 15          | 8           | 7          | 0           |

|----------------------|-----------|-----------|-------------|-------------|-------------|-------------|------------|-------------|

| Word at<br>Address A | Byte at a | address A | Byte at add | dress (A+1) | Byte at add | lress (A+2) | Byte at ad | dress (A+3) |

|                      |           |           | Halfword at | t Address A | Byte at a   | ddress A    | Byte at ad | dress (A+1) |

Figure A3-2 Big-endian byte format

source: DDI0403E.B ARMv7-M Architecture Reference Manual

| MSByte                                      | MSByte-1     | LSByte+1              | LSByte            |

|---------------------------------------------|--------------|-----------------------|-------------------|

|                                             | Word at a    | address A             |                   |

| Halfword at a                               | ddress (A+2) | Halfword at           | address A         |

| Byte at address (A+3) Byte at address (A+2) |              | Byte at address (A+1) | Byte at address A |

Figure A3-3 Little-endian memory system

source: DDI0403E.B ARMv7-M Architecture Reference Manual

Memory access instructions – addressing modes

| Indexing<br>Mode             | Example                 | Action                                                                     | Change in base register |

|------------------------------|-------------------------|----------------------------------------------------------------------------|-------------------------|

| Pre-index with writeback (!) | LDR R0,[R1,#4] !        | R0 = [R1 + 4] (R0 gets the contents of<br>memory location at address R1+4) | R1 = R1 + 4             |

|                              | LDR R0,[R1,R2] !        | R0 = [R1+R2]                                                               | R1 = R1 + R2            |

|                              | LDR R0,[R1,R2,LSL #2] ! | R0 = [R1 + (R2 << 2)]                                                      | R1 = R1 + R2 << 2       |

| Pre-index                    | LDR R0,[R1,#4]          | R0 = [R1 + 4]                                                              | no change               |

|                              | LDR R0,[R1,R2]          | R0 = [R1+R2]                                                               | no change               |

|                              | LDR R0,[R1,R2,LSL #2]   | R0 = [R1 + (R2 << 2)]                                                      | no change               |

| Pre-index                    | LDR R0,[R1],#4          | R0 = [R1]                                                                  | R1 = R1 + 4             |

|                              | LDR R0,[R1],R2          | R0 = [R1]                                                                  | R1 = R1 + R2            |

|                              | LDR R0,[R1],R2,LSL #2   | R0 = [R1]                                                                  | R1 = R1 + R2 << 2       |

BIG IDEAS FOR EVERY SPACE RENESAS

#### **Execution flow control instructions**

| Instruction               | Usage                                                        | Branch Range      |

|---------------------------|--------------------------------------------------------------|-------------------|

| B.N <label></label>       | 16-bit Branch to target address.                             | -256 to 254 bytes |

| B.W <label></label>       | 32-bit Branch to target address.                             | +/-1 MB           |

| CBNZ <label></label>      | Compare and Branch on Nonzero.                               | 0-126 B           |

| CBZ <label></label>       | Compare and Branch on Zero.                                  | 01200             |

| BL <label></label>        | Call a subroutine.                                           | +/–16 MB          |

| BLX <register></register> | Call a subroutine, optionally change instruction set.        | Any               |

| BX <register></register>  | Branch to target address, optionally change instruction set. | Any               |

| TBB                       | TBB: Table Branch, byte offsets.                             | 0-510 B           |

| ТВН                       | TBH: Table Branch, halfword offsets.                         | 0-131070 B        |

BIG IDEAS FOR EVERY SPACE RENESAS

**Miscellaneous instructions**

| Instruction | Usage                                       |

|-------------|---------------------------------------------|

| CPSID       | Change Processor State, Disable Interrupts. |

| CPSIE       | Change Processor State, Enable Interrupts.  |

| DMB         | Data Memory Barrier.                        |

| DSB         | Data Synchronization Barrier.               |

| ISB         | Instruction Synchronization Barrier.        |

| MRS         | Move to Register from Special Register.     |

| MSR         | Move to Special Register from Register.     |

| NOP         | No Operation.                               |

| SVC         | Supervisor Call.                            |

| WFI         | Wait for Interrupt.                         |

### **3.5 – EXCEPTIONS**

The normal flow of execution of a program is to execute the next instruction in memory, unless a Branch, Subroutine Call or Return is executed. Hence, a human processor could execute the same program in the same order.

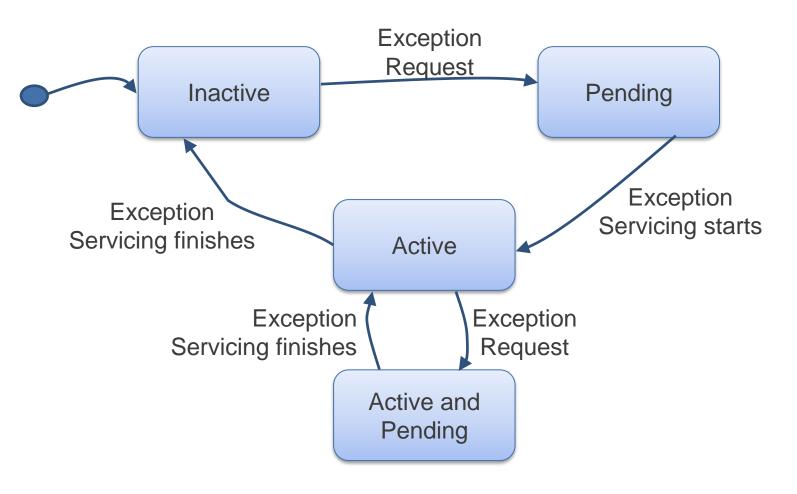

An exception if a break in this normal flow of execution. Such a break can be caused by:

- Hardware interrupt,

- Fault (e.g. memory access error, divide by 0, invalid instruction code),

- Software generate exception.

### **3.5 – EXCEPTIONS**

Exceptions occur **asynchronousl**y, this is, at any point of the execution. They may occur many time and on successive executions of the program they usually occur at different places of this program.

When an exception occurs it must be **serviced**. Meaning that a software routine must either respond to the interrupt request or take steps to resolve or mitigate the fault.

This routine is called: exception handler routine, interrupt service routine, or interrupt handler.

# **3.5 – EXCEPTIONS – INTERRUPTS**

Hardware Interrupts are one of the kind of exceptions.

Interrupts are an efficient way for a peripheral to inform the processor that it requires servicing. If interrupts were not available, the processor would have to periodically poll the peripherals (thus termed **polling**) to check if service is required. Polling is an inefficient technique.

# **3.5 – EXCEPTIONS – INTERRUPTS**

Basic concepts of interrupts:

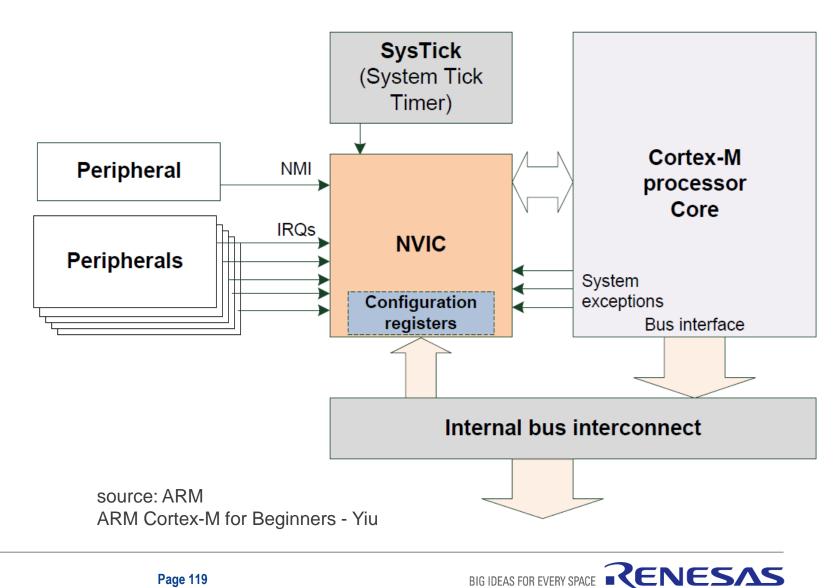

- Peripheral sends an Interrupt Request (IRQ) to an Interrupt Controller

- 2. Interrupt Controller selects the highest priority non-masked interrupt request and informs the core.

- 3. If the priority of the IRQ is sufficiently high, when the instruction currently in execution finishes then the IRQ is serviced.

BIG IDEAS FOR EVERY SPACE

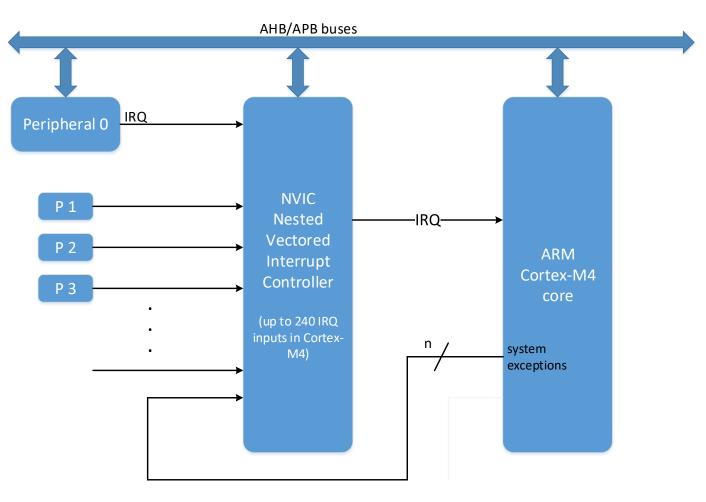

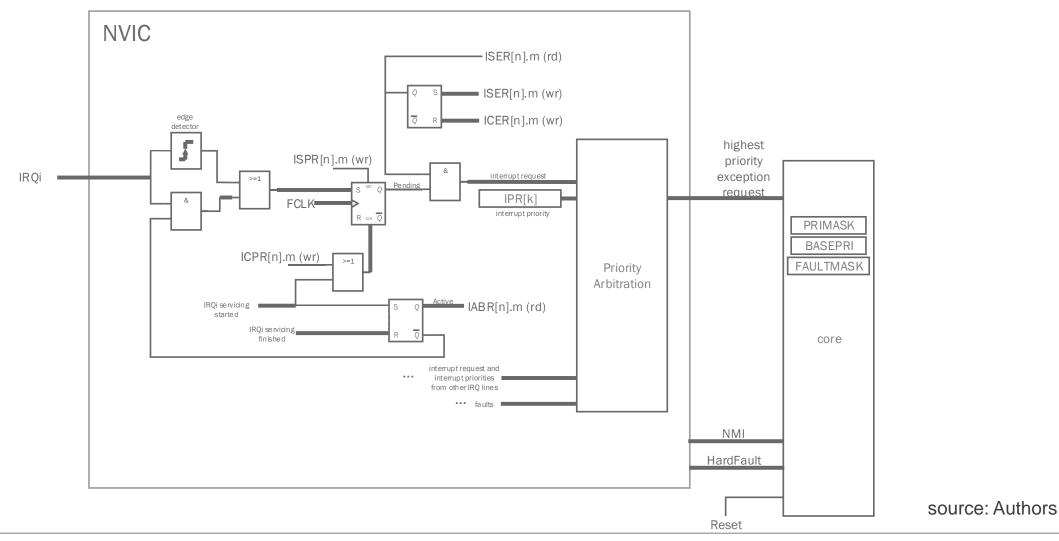

1- An external device, such as a peripheral, requests an interrupt (IRQ) by signaling to the interrupt controller.

The input lines of the interrupt controller (240 in the NVIC of a Cortex-M4) can be either level sensitive of edge sensitive.

2- Upon receiving an IRQi (hardware signal on input i of the interrupt controller - IC) then the IC performs two checks:

- a) if input i is masked or not;

- b) if there is another request (IRQj on input j) already being sent to the processor.

If IRQi is not masked and if its priority is higher than IRQj's priority (or no request is currently being sent to the processor)

then IRQi is forwarded to the processor.

- 3- The processor, upon receiving an IRQ verifies if its priority is sufficiently high:

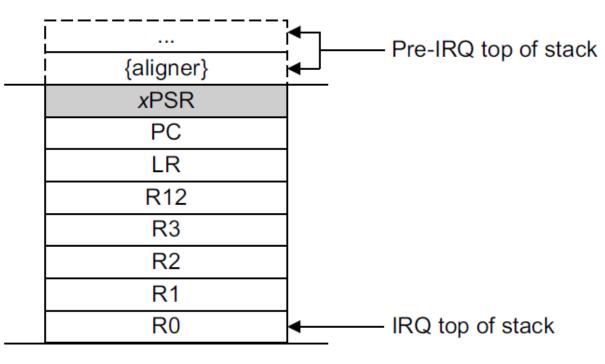

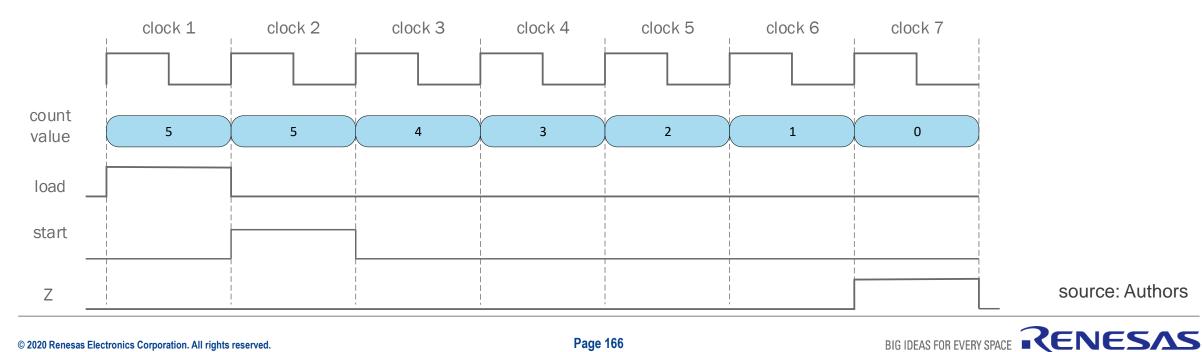

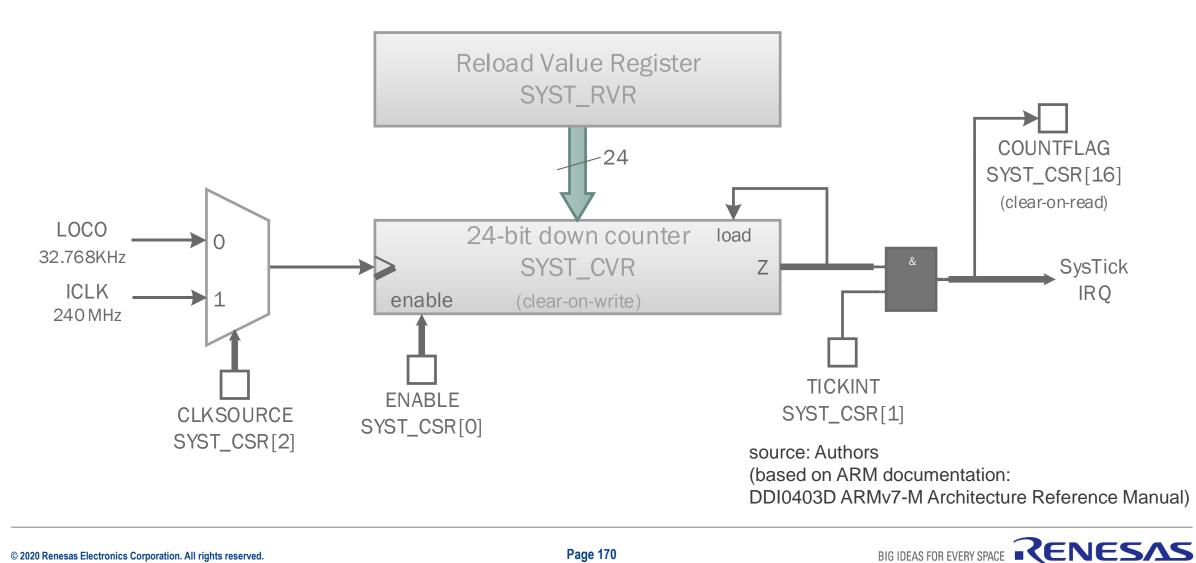

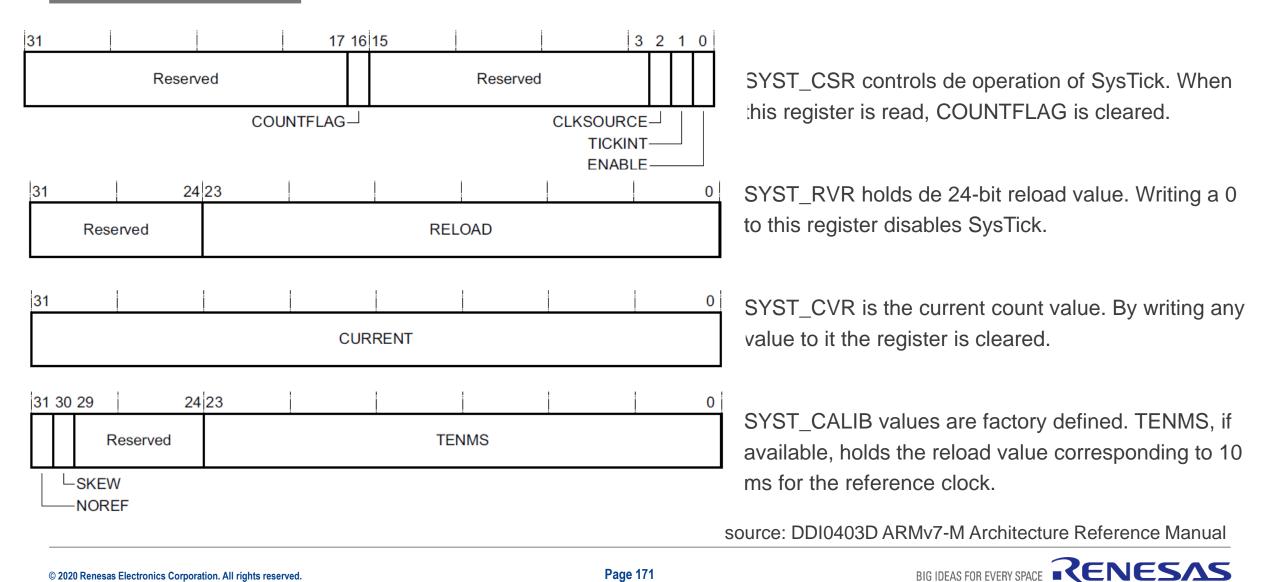

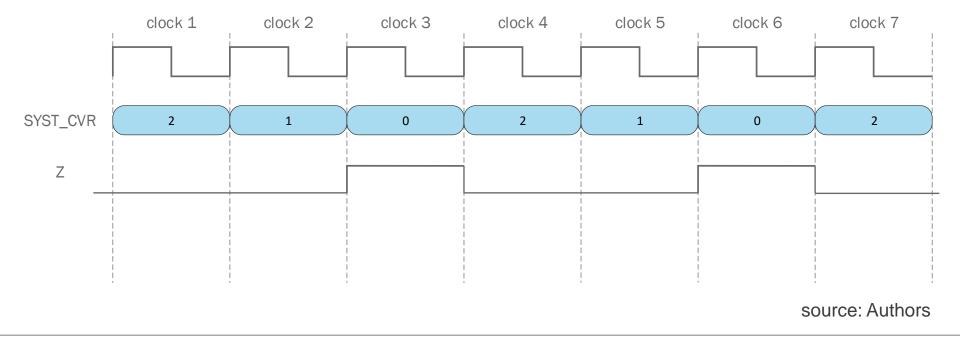

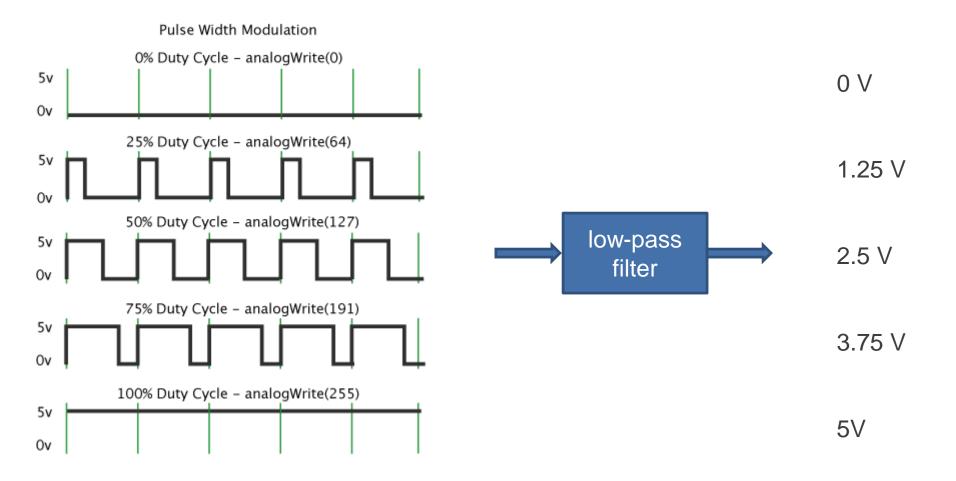

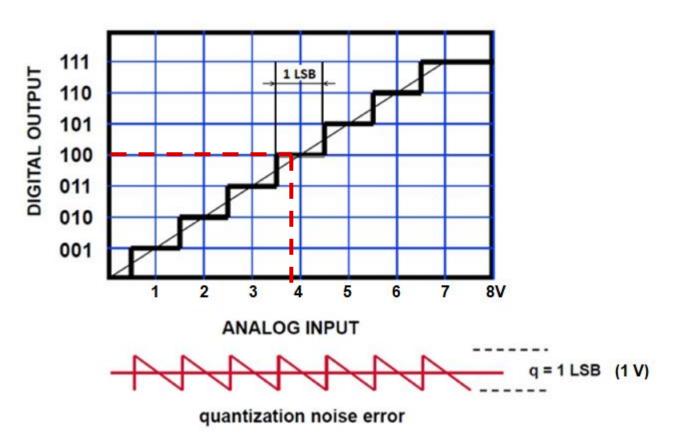

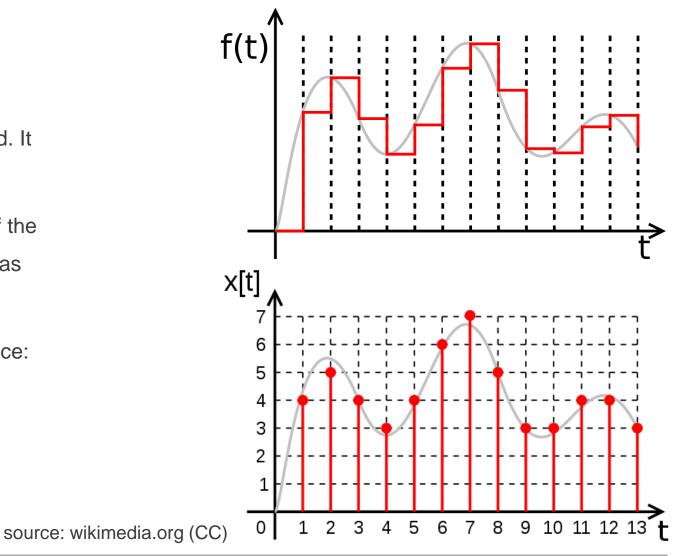

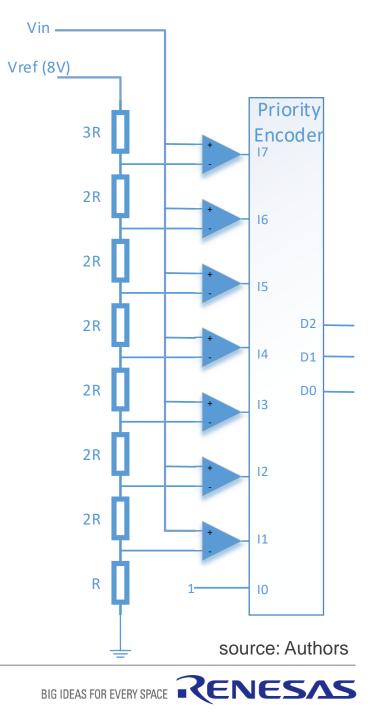

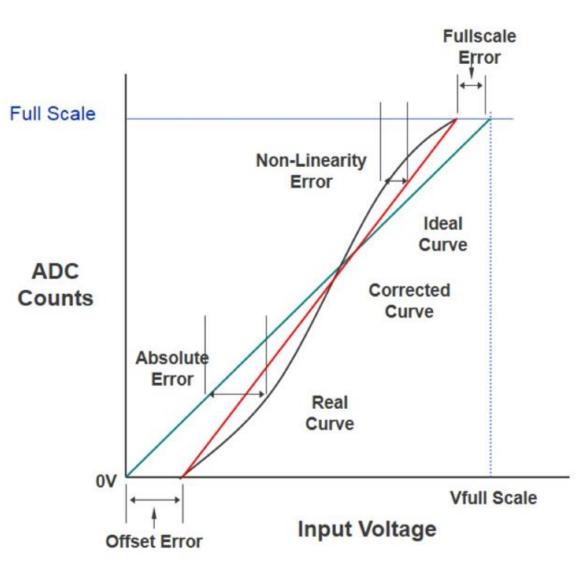

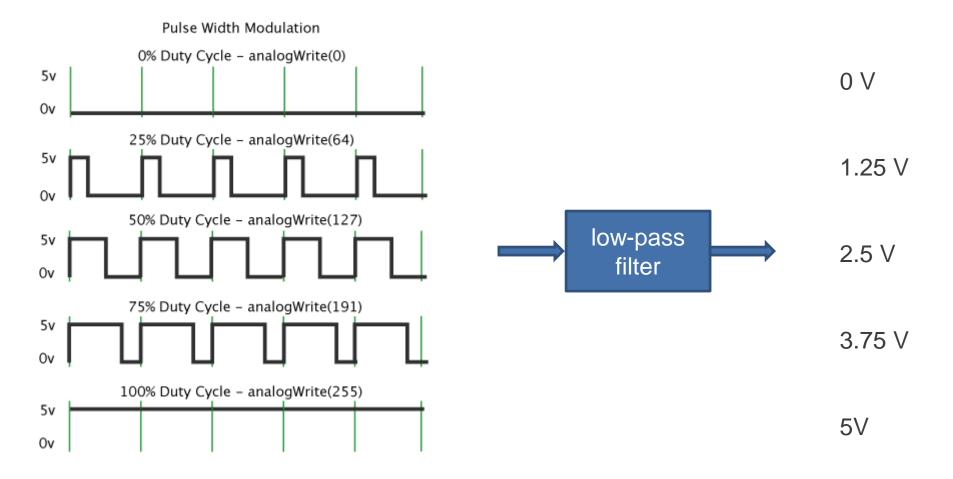

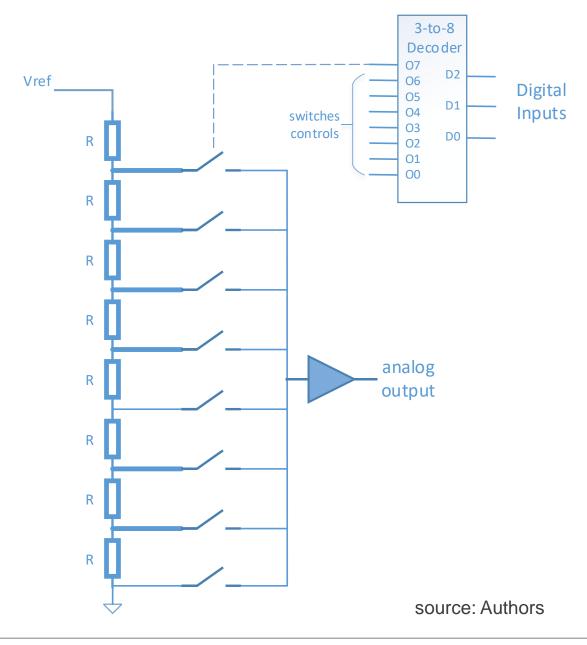

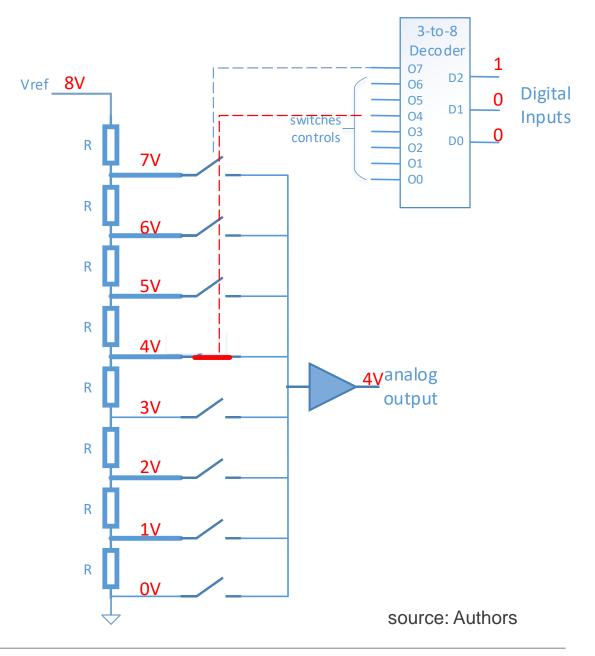

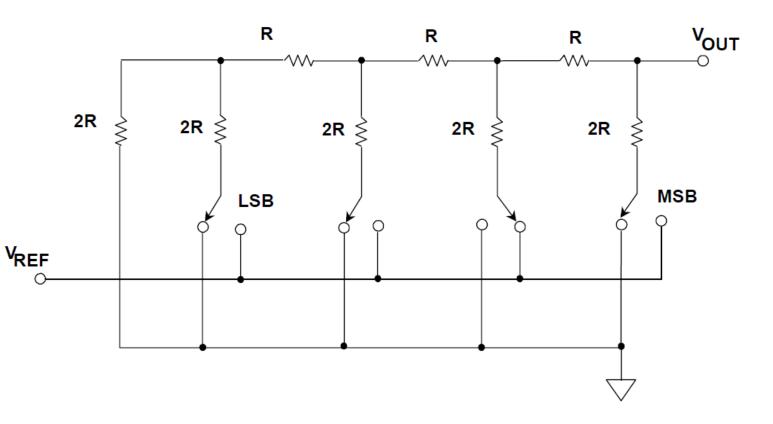

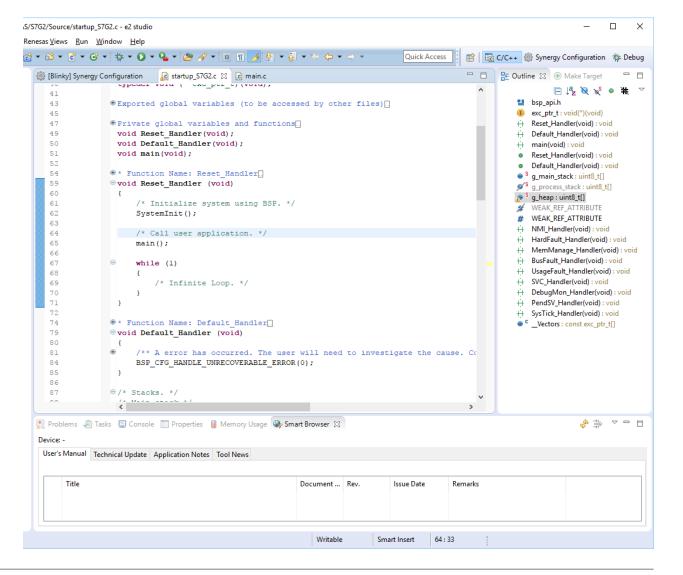

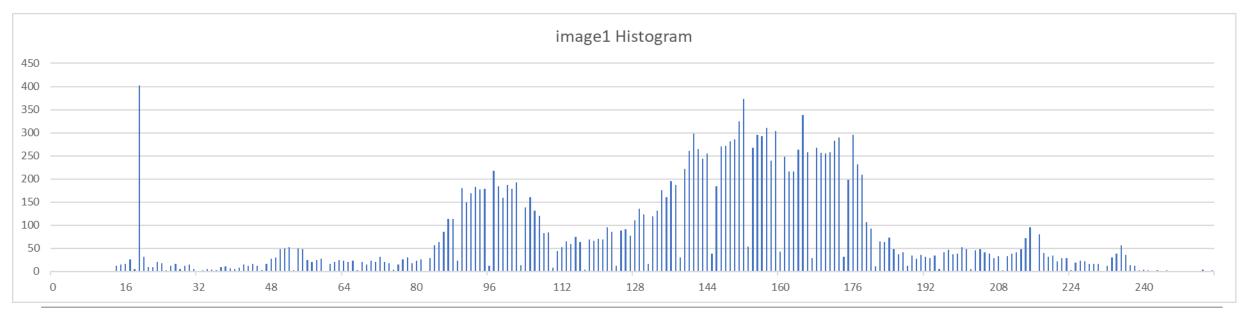

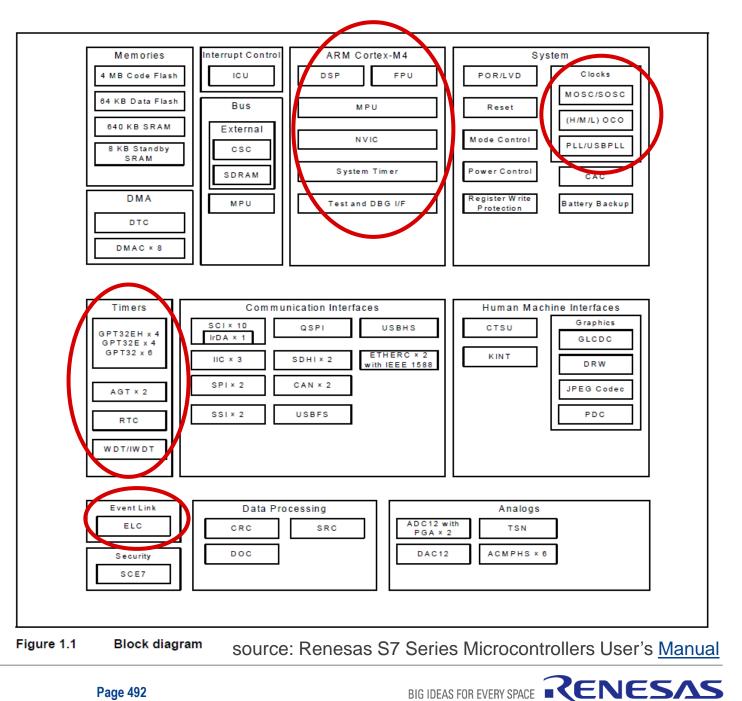

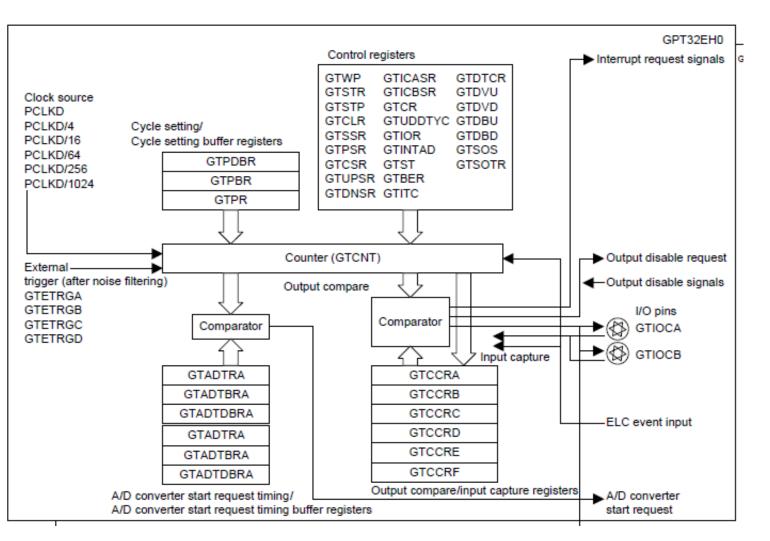

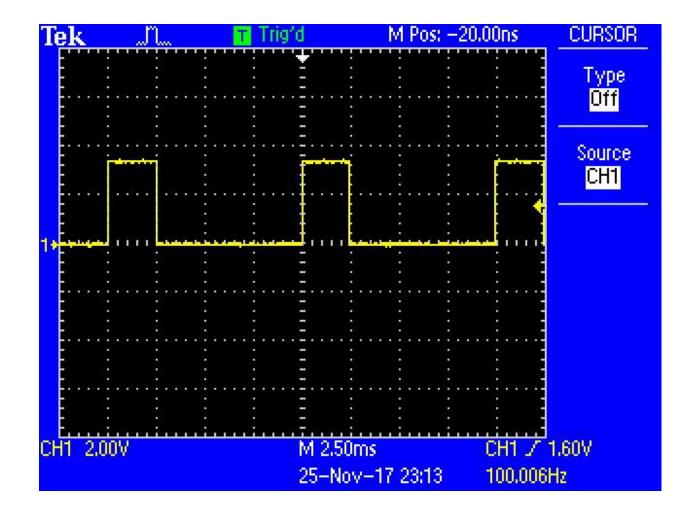

- a) PRIMASK and FAULTMASK, when set, impose a priority level of 0 or -1 respectively. Hence, when FAULTMASK is set, all exceptions from 3 on are masked.